#### Lecture 21

Analog-to-Digital Converters (continued)

- Residue Type ADCs

- · Two-Step flash

- Pipelined ADCs

- Concept and basics of the architecture

- Effect of building block non-idealities on overall ADC performance

- Sub-ADC

- Sub-DAC

- · Gain stage

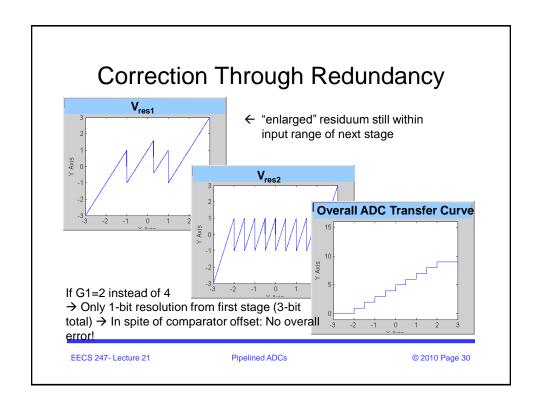

- Error correction by adding redundancy

- Digital calibration

- Correction for inter-stage gain nonlinearity

EECS 247 Lecture 21:

Data Converters: Nyquist Rate ADCs

© 2010 Page 1

### **ADC Architectures**

- Slope type converters

- · Successive approximation

- Flash

- · Interpolating & Folding

- Residue type ADCs

- Two-step Flash

- Pipelined ADCs

- \_

- · Time-interleaved / parallel converter

- Oversampled ADCs

EECS 247 Lecture 21:

Data Converters- Nyquist Rate ADCs

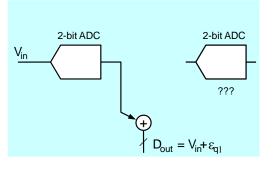

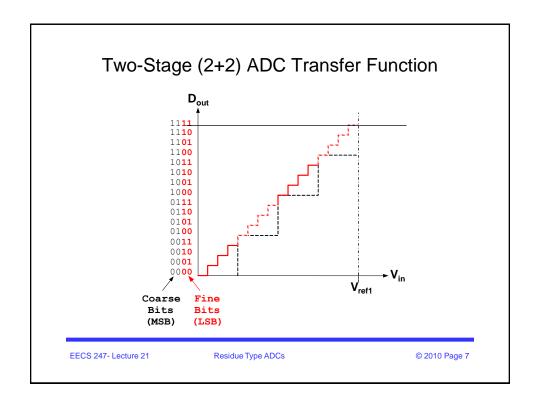

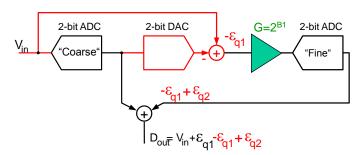

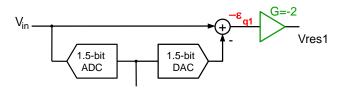

Two-Step Example: (2+2)Bits

- Using only one ADC: output contains large quantization error

- "Missing voltage" or "residue" (  $\mbox{-}\epsilon_{q1})$

- Idea: Use second ADC to quantize and add - $\epsilon_{\rm q1}$

EECS 247- Lecture 21

Residue Type ADCs

© 2010 Page 3

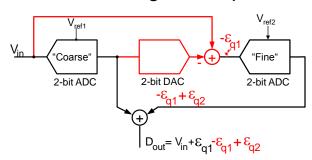

#### Two Stage Example

- · Use DAC to compute missing voltage

- · Add quantized representation of missing voltage

- Why does this help? How about  $\epsilon_{q2}$ ?

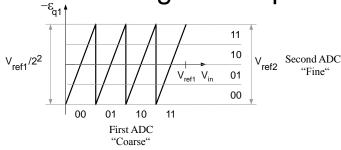

Since maximum voltage at input of the  $2^{nd}$  ADC is  $V_{ref1}/4$  then for  $2^{nd}$  ADC  $V_{ref2}=V_{ref1}/4$  and thus  $\epsilon_{q2}=\epsilon_{q1}/4=V_{ref1}/16$   $\rightarrow$  4bit overall resolution

EECS 247- Lecture 21

Residue Type ADCs

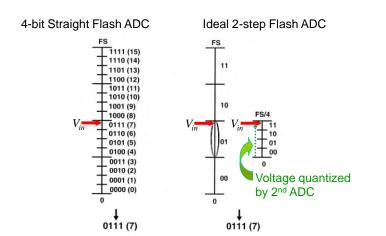

### Two Step (2+2) Flash ADC

EECS 247- Lecture 21

Residue Type ADCs

© 2010 Page 5

## Two Stage Example

- Fine ADC is re-used 2<sup>2</sup> times

$$\varepsilon_{q2} = \frac{V_{ref2}}{2^2} = \frac{V_{ref1}}{2^2 \cdot 2^2}$$

EECS 247- Lecture 21

Residue Type ADCs

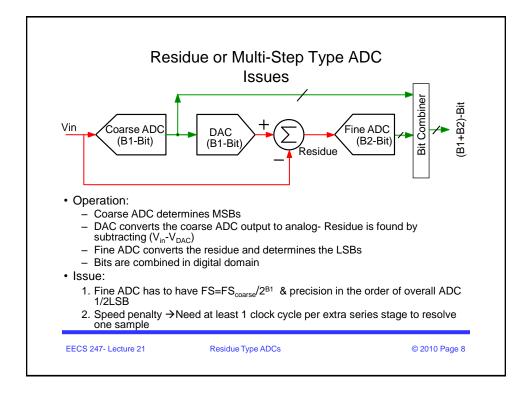

## Solution to Issue (1) Reducing Precision Required for Fine ADC

- Accuracy needed for fine ADC relaxed by introducing inter-stage gain

- Example: By adding gain of x(G=2<sup>B1</sup>=4) prior to fine ADC in (2+2)bit case, precision required for fine ADC is reduced to 2-bit only!

- Additional advantage- coarse and fine ADC can be identical stages

EECS 247- Lecture 21

Residue Type ADCs

© 2010 Page 9

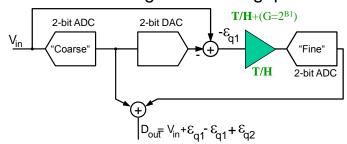

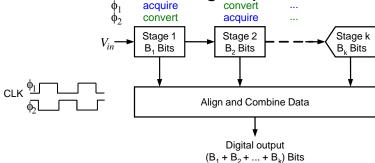

## Solution to Issue (2) Increasing ADC Throughput

- Conversion time significantly decreased by employing T/H between stages

- All stages busy at all times → operation concurrent

- During one clock cycle coarse & fine ADCs operate concurrently:

- First stage samples/converts/generates residue of input signal sample # n

- While  $2^{\rm nd}$  stage samples/converts residue associated with sample # n-1

EECS 247- Lecture 21

Residue Type ADCs

## Residue Type ADCs

- · Two-Step flash

- → Pipelined ADCs

- Basic operation

- Effect of sub-ADC, sub-DAC, gain stage non-idealities on overall ADC performance

- · Error correction by adding redundancy

- · Digital calibration

- · Correction for inter-stage gain nonlinearity

- Implementation

- · Practical circuits

- · Stage scaling

- · Combining the bits

- · Stage implementation

- Circuits

- Noise budgeting

- · How many bits per stage?

EECS 247- Lecture 21

**Pipelined ADCs**

© 2010 Page 11

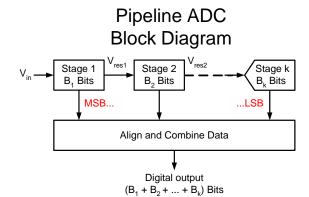

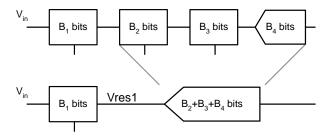

- Idea: Cascade several low resolution stages to obtain high overall resolution (e.g. 10bit ADC can be built with series of 10 ADCs each 1-bit only!)

- Each stage performs coarse A/D conversion and computes its quantization error, or "residue"

- All stages operate concurrently

EECS 247- Lecture 21

Pipelined ADCs

# $\begin{array}{c} \text{Pipeline ADC} \\ \text{Concurrent Stage Operation} \\ _{\phi_1} \quad _{\text{acquire}} \quad _{\text{convert}} \quad ... \end{array}$

- · Stages operate on the input signal like a shift register

- New output data every clock cycle, but each stage introduces at least ½ clock cycle latency

EECS 247- Lecture 21

**Pipelined ADCs**

© 2010 Page 13

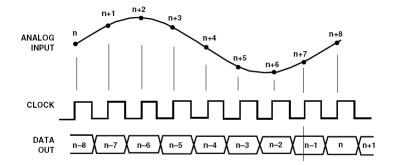

# Pipeline ADC Latency

Note: One conversion per clock cycle & 8 clock cycle latency

[Analog Devices, AD 9226 12bit ADC Data Sheet]

EECS 247- Lecture 21

Pipelined ADCs

## Pipelined ADC Characteristics

- Number of components (stages) grows linearly with resolution

- Pipelining

- Trading latency for overall component count

- Latency may be an issue in e.g. control systems

- Throughput limited by speed of one stage → Fast

- Versatile: 8...16bits, 1...400MS/s

- One important feature of pipelined ADCs: many analog circuit non-idealities can be corrected digitally

EECS 247- Lecture 21

**Pipelined ADCs**

© 2010 Page 15

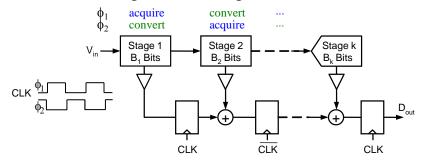

## Pipeline ADC Digital Data Alignment

Digital shift register aligns sub-conversion results in time

EECS 247- Lecture 21

Pipelined ADCs

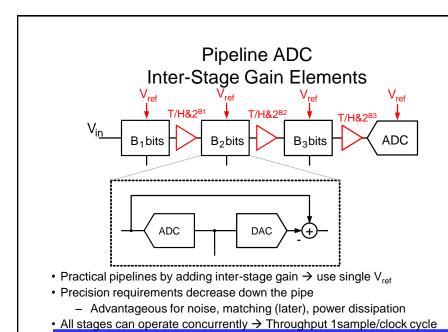

### **Cascading More Stages**

- · LSB of last stage becomes very small

- · All stages need to have full precision

- Impractical to generate several V<sub>ref</sub>

EECS 247- Lecture 21

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 17

© 2010 Page 18

Pipelined ADCs

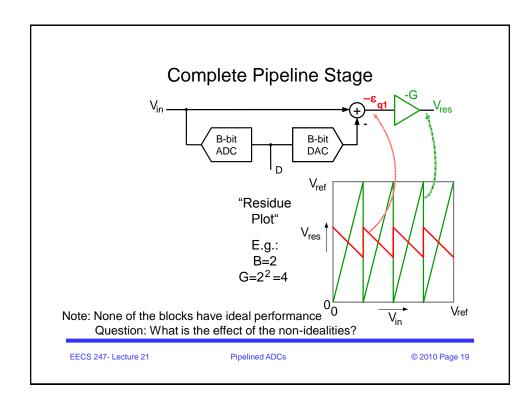

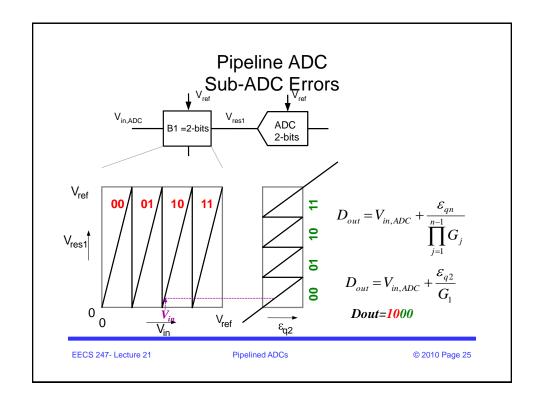

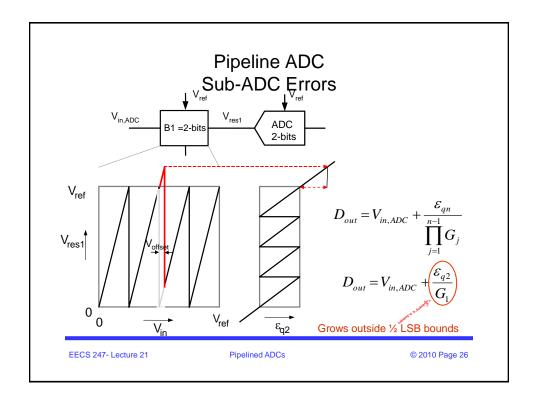

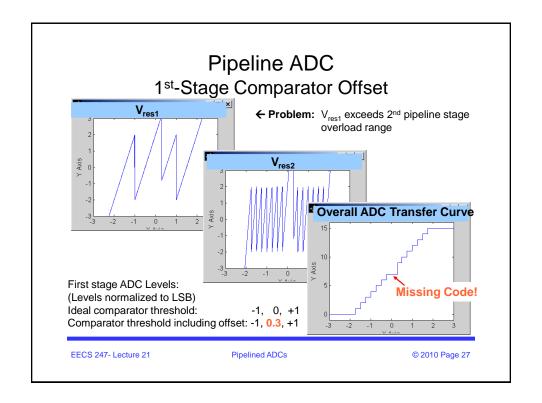

### Pipeline ADC Errors

- Non-idealities associated with sub-ADCs, sub-DACs and gain stages → error in overall pipeline ADC performance

- Need to find means to tolerate/correct errors

- · Important sources of error

- Sub-ADC errors- comparator offset

- Gain stage offset

- Gain stage gain error

- Sub-DAC error

EECS 247- Lecture 21

Pipelined ADCs

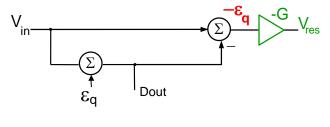

## Pipeline ADC Single Stage Model

$$V_{res} = GxE_q$$

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 21

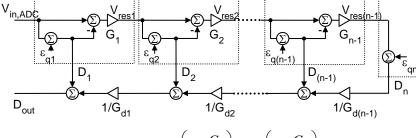

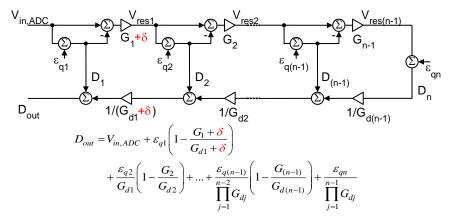

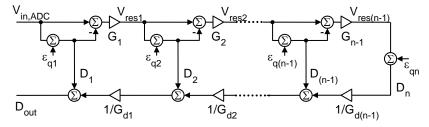

### Pipeline ADC Multi-Stage Model

$$D_{out} = V_{in,ADC} + \varepsilon_{ql} \left( 1 - \frac{G_l}{G_{dl}} \right) + \frac{\varepsilon_{q2}}{G_{dl}} \left( 1 - \frac{G_2}{G_{d2}} \right) + \dots + \frac{\varepsilon_{q(n-l)}}{\prod_{j=l}^{n-2} G_{dj}} \left( 1 - \frac{G_{(n-l)}}{G_{d(n-l)}} \right) + \frac{\varepsilon_{qn}}{\prod_{j=l}^{n-l} G_{dj}}$$

EECS 247- Lecture 21

Pipelined ADCs

#### Pipeline ADC Model

• If the "Analog" and "Digital" gain/loss is precisely matched:

$$D_{out} = V_{in,ADC} + \frac{\varepsilon_{qn}}{\prod\limits_{j=1}^{n-1} G_j} \quad \text{where} \quad \varepsilon_{qn} = \frac{V_{ref}}{2^{Bn}} \quad \& Bn = \# \text{ of bits in final stage}$$

$$D.R. = 20 \log \frac{rms \ FS \ Signal}{rms \ Quant. \ Noise} = 20 \log \frac{\frac{V_{ref}}{2\sqrt{2}}}{\sqrt{12 \times 2^{B_n}} \prod_{j=1}^{n-1} G_j} = 20 \log \left( \sqrt{\frac{3}{2}} \times 2^{B_n} \times \prod_{j=1}^{n-1} G_j \right)$$

$$B_{ADC} \sim \log_2\left(2^{B_n} \times \prod_{j=1}^{n-1} G_j\right)$$

$$B_{ADC} \approx B_n + \log_2 \prod_{j=1}^{n-1} G_j$$

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 23

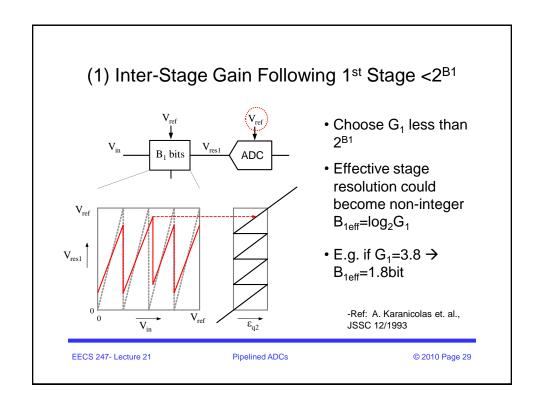

## Pipeline ADC Observations

- The aggregate ADC resolution is independent of sub-ADC resolution!

- Effective stage resolution B<sub>j</sub>=log<sub>2</sub>(G<sub>j</sub>)

- Overall conversion error does not (directly) depend on sub-ADC errors!

- Only error term in D<sub>out</sub> contains quantization error associated with the last stage

- So why do we care about sub-ADC errors?

Go back to two stage example

EECS 247- Lecture 21

Pipelined ADCs

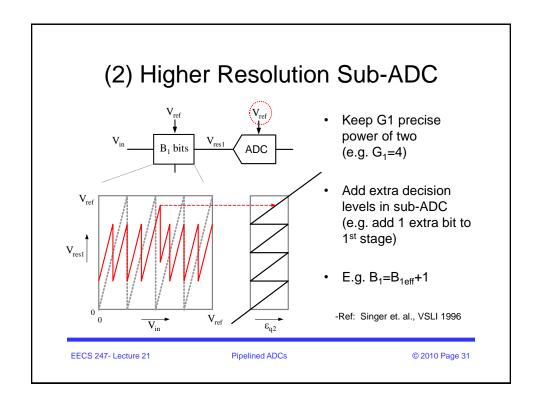

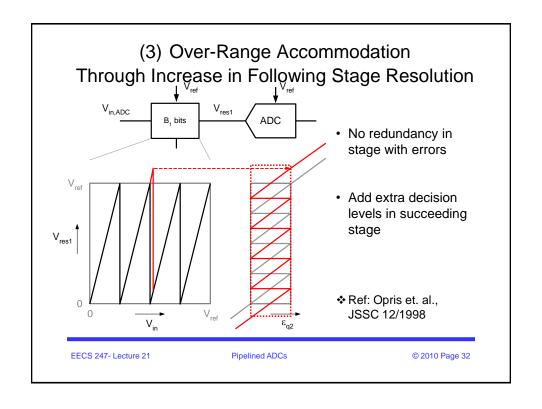

## Pipeline ADC Three Ways to Deal with Sub-ADC Errors

- All involve "sub-ADC redundancy"

- Redundancy in stage that produces errors

- Choose gain for residue to be processed by the  $2^{nd}$  stage  $< 2^{B1}$

- Higher resolution sub-ADC & sub-DAC

- Redundancy in succeeding stage(s)

EECS 247- Lecture 21

Pipelined ADCs

### Redundancy

- The preceding analysis applies to any stage in an n-stage pipeline

- Can always perceive a multi-stage pipelined ADC as a single stage + backend ADC

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 33

© 2010 Page 34

## Redundancy

- In literature, sub-ADC redundancy schemes are often called "digital correction" – a misnomer!

- No error correction takes place

- We can tolerate sub-ADC errors as long as:

- -The residues stay "within the box", or

- –Another stage downstream "returns the residue to "within the box" before it reaches last quantizer

- Let's calculate tolerable errors for popular "1.5 bits/stage" topology

EECS 247- Lecture 21 Pipelined ADCs

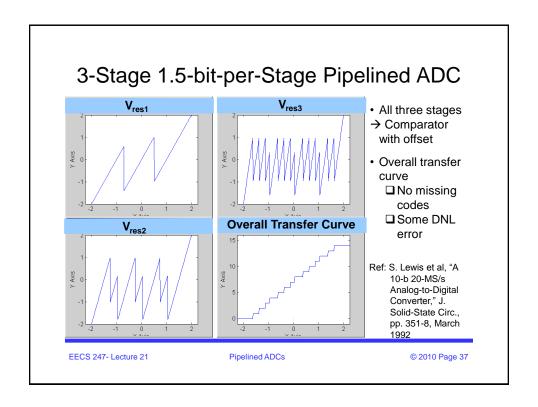

#### 1.5-Bit/Stage Pipelined ADC

- G=-2

- Effective bit/stage  $\rightarrow$  B<sub>eff</sub>=log<sub>2</sub>|G|=log<sub>2</sub>2=1

- Actual bit/stage  $\rightarrow$  B=log<sub>2</sub>(2+1)=1.589...

- 1bit/stage + 0.5bit → redundancy

- ❖ Ref: Lewis et. al., JSSC 3/1992

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 35

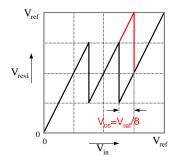

#### 1.5 Bits/Stage Example

- Comparators threshold levels placed strategically

- G=2

- B<sub>eff</sub>=log<sub>2</sub>G=log<sub>2</sub>2=1

- B=log<sub>2</sub>(2+1)=1.589...

- 0.5bit→ redundancy

❖ Ref: Lewis et. al., JSSC 3/1992

EECS 247- Lecture 21

Pipelined ADCs

#### Pipeline ADC Errors

- Non-idealities associated with sub-ADCs, sub-DACs and gain stages → error in overall pipeline ADC performance

- Need to find means to tolerate/correct errors

- Important sources of error

- Sub-ADC errors- comparator offset

- Gain stage offset

- Gain stage error

- Sub-DAC error

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 39

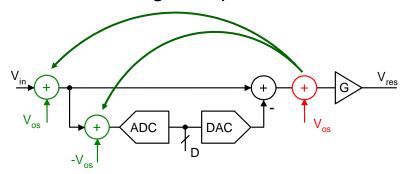

#### Inter-Stage Amplifier Offset

- Input referred converter offset usually no problem

- Equivalent sub-ADC offset accommodated through adequate redundancy

EECS 247- Lecture 21

Pipelined ADCs

#### Pipeline ADC Errors

- Non-idealities associated with sub-ADCs, sub-DACs and gain stages → error in overall pipeline ADC performance

- Need to find means to tolerate/correct errors

- · Important sources of error

- Sub-ADC errors- comparator offset

- Gain stage offset

- Gain stage gain error

- Sub-DAC error

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 41

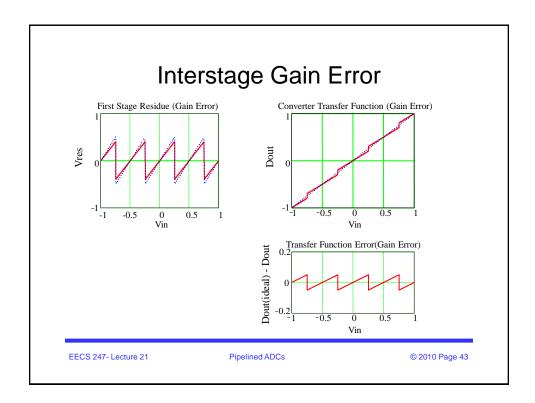

### Gain Stage Gain Error

- Resolution is function of log<sub>2</sub>G therefore error in G affects resolution →Small amount of gain error can be tolerated

EECS 247- Lecture 21

Pipelined ADCs

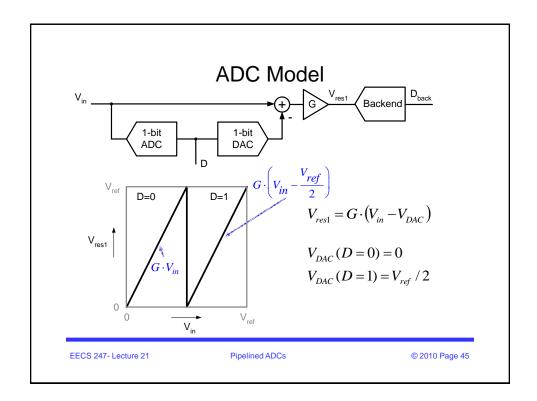

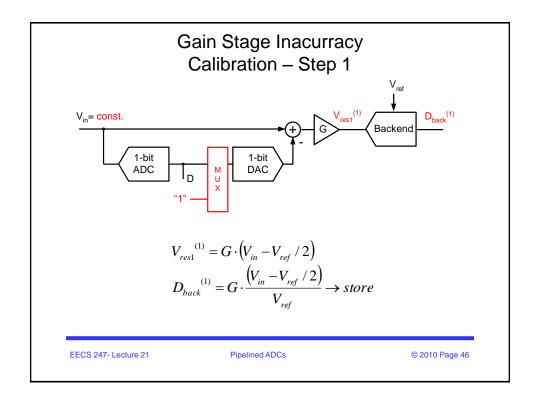

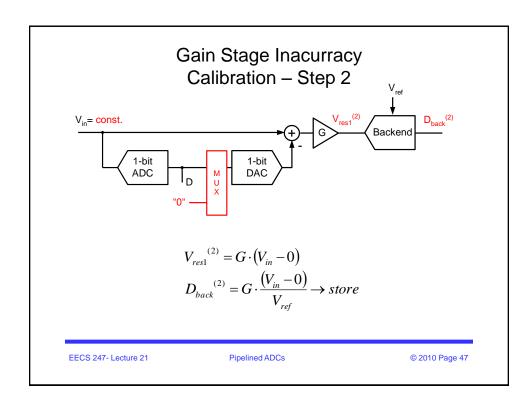

## Gain Stage Gain Inaccuracy

- Gain error can be compensated in digital domain – "Digital Calibration"

- Problem: Need to measure/calibrate digital correction coefficient

- Example: Calibrate 1-bit first stage

- Objective: Measure G in digital domain

EECS 247- Lecture 21 Pipelined ADCs © 2010 Page 44

#### Gain Stage Inacurracy Calibration – Evaluate

To minimize the effect of backend ADC noise → perform measurement several times and take the average

EECS 247- Lecture 21

Pipelined ADCs

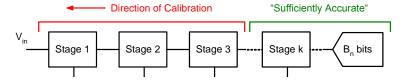

#### **Accuracy Bootstrapping**

$$D_{out} = V_{in,ADC} + \mathcal{E}_{q1} \Biggl( 1 - \frac{G_1}{G_{d1}} \Biggr) + \underbrace{\frac{\mathcal{E}_{q2}}{G_{d2}}} \Biggl( 1 - \frac{G_2}{G_{d2}} \Biggr) + \dots + \underbrace{\frac{\mathcal{E}_{q(n-1)}}{G_{dj}}} \Biggl( 1 - \frac{G_{(n-1)}}{G_{d(n-1)}} \Biggr) + \underbrace{\frac{\mathcal{E}_{qn}}{G_{dn}}} \Biggr) + \dots + \underbrace{\frac{\mathcal{E}_{q(n-1)}}{G_{dj}}} \Biggl( 1 - \underbrace{\frac{G_{(n-1)}}{G_{d(n-1)}}} \Biggr) + \underbrace{\frac{\mathcal{E}_{qn}}{G_{dn}}} \Biggr) + \dots + \underbrace{\frac{\mathcal{E}_{q(n-1)}}{G_{dj}}} \Biggl( 1 - \underbrace{\frac{G_{(n-1)}}{G_{d(n-1)}}} \Biggr) + \underbrace{\frac{\mathcal{E}_{qn}}{G_{dn}}} \Biggr) + \underbrace{\frac{\mathcal{E}_$$

· Highest sensitivity to gain errors in front-end stages

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 49

## "Accuracy Bootstrapping"

#### Ref:

A. N. Karanicolas et al. "A 15-b 1-Msample/s digitally self-calibrated pipeline ADC," *IEEE J. Of Solid-State Circuits*, pp. 1207-15, Dec. 1993

E. G. Soenen et al., "An architecture and an algorithm for fully digital correction of monolithic pipelined ADCs," TCAS II, pp. 143-153, March 1995

L. Singer et al., "A 12 b 65 MSample/s CMOS ADC with 82 dB SFDR at 120 MHz," ISSCC 2000, Digest of Tech. Papers., pp. 38-9 (calibration in opposite direction!)

EECS 247- Lecture 21

Pipelined ADCs

### Pipeline ADC Errors

- Non-idealities associated with sub-ADCs, sub-DACs and gain stages → error in overall pipeline ADC performance

- Need to find means to tolerate/correct errors

- Important sources of error

- Sub-ADC errors- comparator offset

- Gain stage offset

- Gain stage error

- Sub-DAC error

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 51

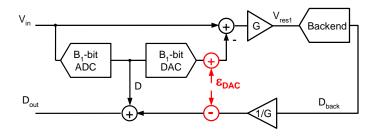

### **DAC Errors**

- · Can be corrected digitally as well

- Same calibration concept as gain errors

- → Vary DAC codes & measure errors via backend ADC

EECS 247- Lecture 21

Pipelined ADCs

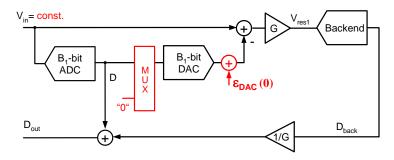

## DAC Calibration - Step 1

•  $\varepsilon_{DAC}(0)$  equivalent to offset - ignore

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 53

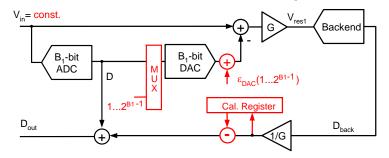

## DAC Calibration - Step 2...2<sup>B1</sup>

- Stepping through DAC codes 1...2<sup>B1-1</sup> yields all incremental correction values

- Measurements repeated and averages to account for variance associated with noise

EECS 247- Lecture 21

Pipelined ADCs

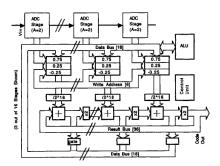

#### Pipeline ADC Example: Calibration Hardware

Above block diagram may seem extensive however, in current fine-line CMOS technologies digital portion of a pipeline ADCs consume insignificant power and area compared to the analog sections

Ref: E. G. Soenen et al., "An architecture and an algorithm for fully digital correction of monolithic pipelined ADCs," TCAS II, pp. 143-153, March 1995

EECS 247- Lecture 21

Pipelined ADCs

© 2010 Page 55

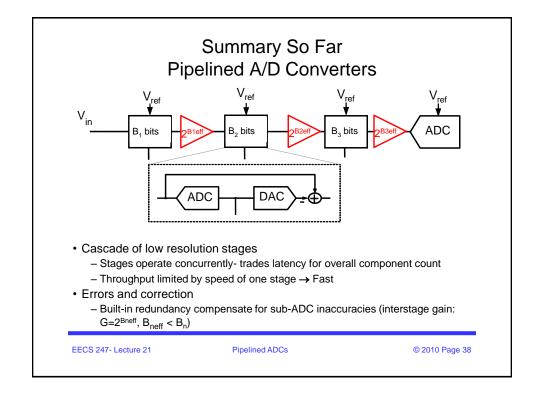

## Summary So Far Pipelined A/D Converters

- · Cascade of low resolution stages

- By adding inter-stage gain= 2<sup>Beff</sup>

- No need to scale down Vref for stages down the pipe

- Reduced accuracy requirement for stages coming after stage 1

- Addition of Track & Hold function to interstage-gain →

- Stages can operate concurrently→

- Throughput increased to as high as one sample per clock cycle

- · Latency function of number of stages & conversion-per-stage

- Correction for circuit non-idealities

- Built-in redundancy compensate for sub-ADC inaccuracies such as comparator offset (interstage gain:  $G=2^{Bneff}$ ,  $B_{neff} < B_n$ )

- Error associated with gain stage and sub-DAC calibrated out

EECS 247- Lecture 21 Pipelined ADCs