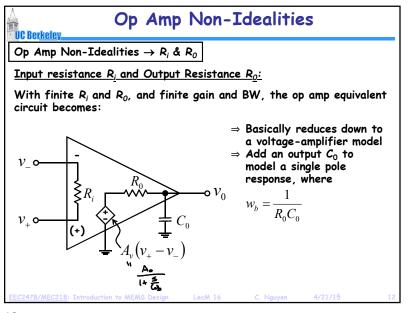

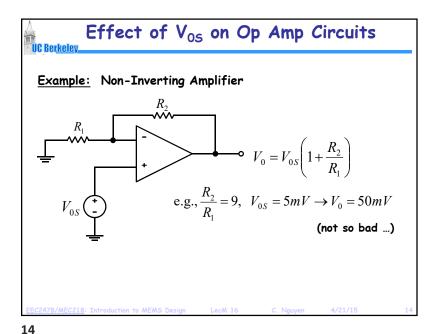

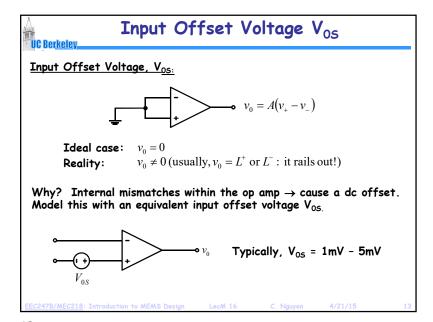

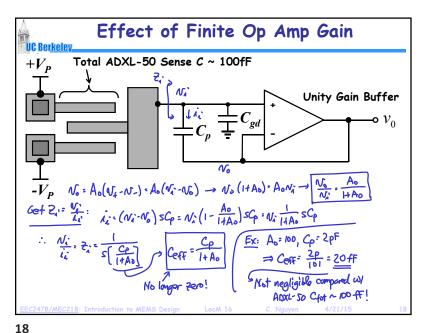

**UC Berkeley** \* Actual op amps, of course, are not ideal; rather, they ... Senerate noise ♦ Have finite gain, A<sub>0</sub> \$ Have finite bandwidth, ω<sub>b</sub> \$ Have finite input resistance, R. ♦ Have finite input capacitance, C<sub>i</sub> Have finite output resistance, R. ♦ Have an offset voltage V<sub>os</sub> between their (+) and (-) terminals ♦ Have input bias currents  $\$  Have an offset  $I_{OS}$  between the bias currents into the (+) and (-) terminals \$ Have finite output swing (governed by the supply voltage used, -L to +L) \* And what's worse: All of the above can be temperature (or

Actual Op Amps Are Not Ideal

Finite Op Amp Gain and Bandwidth **UC** Berkeley • For an ideal op amp:  $A = \infty$ • In reality, the gain is given by: A(s) = -• For ω>>ω<sub>h</sub>:  $A(s) \approx \frac{A_0}{(s/\omega_b)} = \frac{A_0\omega_b}{s} = \frac{\omega_T}{s}$ Integrator w/ time const. 1/ $\omega_T$  $A(j\omega)$  This pole actually designed in for some op amps.  $20\log(A_0)$ Open-loop response of the amplifier. \_ 20dB/dec Unity gain 3 dB frequency:  $\omega_T = A_0 \omega_h$ frequency

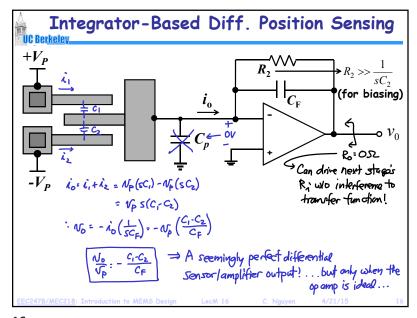

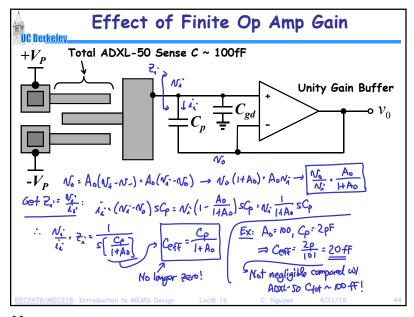

Integrator-Based Diff. Position Sensing UC Berkeley  $+V_{P}$ (for biasing) 8:05Z Can drive next stage's  $-V_P \quad \dot{l_0} = \dot{l_1} + \dot{l_2} = N_P(\varsigma C_1) - N_P(\varsigma C_2)$ R: wo interference to  $\cdot \sqrt{V_{p}} = -\sqrt{V_{p}} \left( \frac{C_{1} - C_{2}}{C_{p}} \right) = -\sqrt{V_{p}} \left( \frac{C_{1} - C_{2}}{C_{p}} \right)$ transfer function!  $\frac{C_1 - C_2}{C_F}$   $\Rightarrow$  A seemingly perfect differential sensor/amplifier output?...but only when the open is ideal...

11

otherwise environmentally) dependent!

12

13

16

**17**

19

то

250 nm CMOS Cross-Section UC Berkeley 2<sup>nd</sup> Level Metal Interconnect (e.g., Cu) 1st Level Metal Interconnect (e.g., Al) LPCVD SiO2 Polysilicon Ġate CVD Tungsten TiN Local Interconnect LOCOS Oxidation N Well - PMOS Substrate P Well - NMOS Subs Lightly Doped Drain (LDD) TiSi<sub>2</sub> Contact Barrier 28 masks and a lot more Silicon Substrate complicated than MEMS!

20

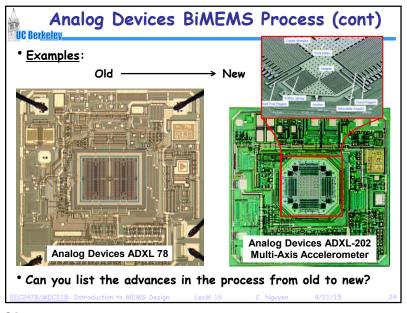

Analog Devices BiMEMS Process **UC Berkeley** • Interleaved MEMS and 4 µm BiMOS processes (28 masks) Diffused n+ runners used to interconnect MEMS & CMOS \* Relatively deep junctions allow for MEMS poly stress anneal Used to manufacture the ADXL-50 accelerometer and Analog Devices family of accelerometers SENSOR POLYSI ☐ SILICON LPCVD NITRIDE SPACER LTO PLASMA OXIDE OXIDE BPSG SENSOR POLYSI PLASMA NITRIDE ZZ LTO POLYSI METAL

24

28

30

IIC Berkeley

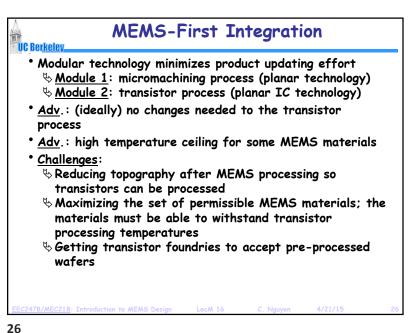

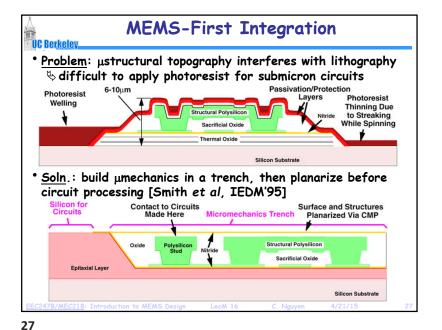

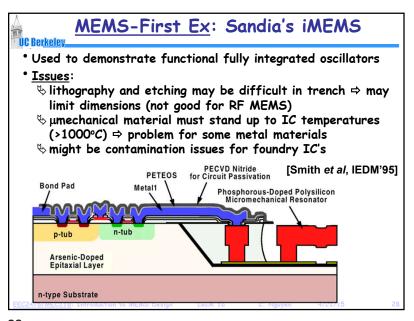

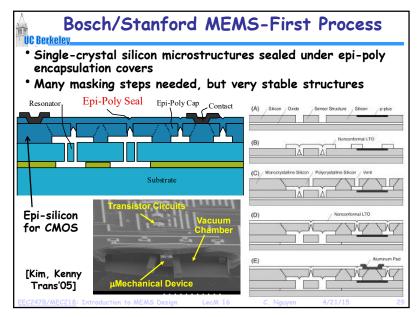

#### Problems With MEMS-First

- $^{\bullet}$  Many masking steps needed, plus CMP required  $\rightarrow$  cost can grow if you're not careful

- Processes using trenches sacrifice lithographic resolution in microstructures

- MEMS must withstand transistor processing temperatures

Precludes the use of structural materials with low temperature req'mts: metals, polymers, etc.

- Exotic MEMS (e.g., ZnO) that can contaminate transistors during their processing are not permissible

thus, not truly modular

- Foundry acceptance not guaranteed and might be rare

EEC247B/MEC218: Introduction to MEMS Design LecM 16 C. Nguyen 4/21/15

29

# Foundry Acceptance of MEMS-First?

UC Berkeley\_

- Is a CMP'ed silicon surface sufficiently pure for fabrication of aggressively scaled transistors? How about if an oxide is grown over the CMP'ed surface and removed via a wet etch to yield a "pristine" surface?

- Is epi silicon grown as part of a sealing process sufficiently pure for fabrication of aggressively scaled transistors?

- CMOS is many times more difficult to run than MEMS

- \$ Feature sizes on the nm scale for billions of devices

- ♥ Contamination a big issue: many foundries may not accept pre-processed wafers for contamination reasons

- Many foundries will not accept any pre-processed wafers, MEMS or not → just can't guarantee working transistor circuits with unknowns in starting silicon

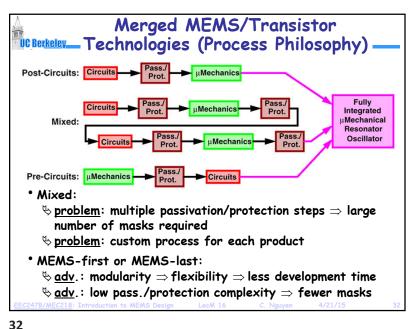

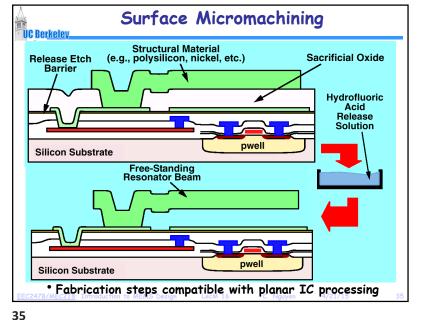

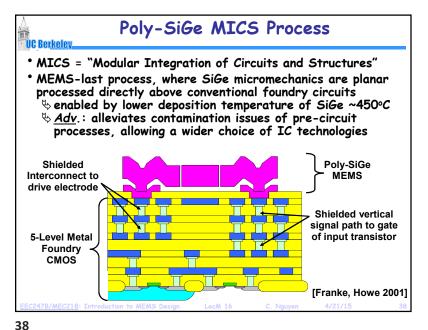

# **MEMS-Last Integration**

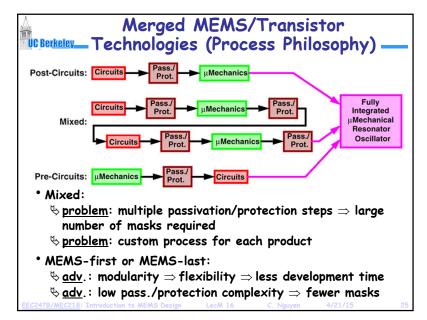

- Modular technology minimizes product updating effort

- ♦ Module 1: transistor process (planar IC technology) ♦ Module 2: micromachining process (planar technology)

- \* Adv.: foundry friendly

- $\checkmark$  Virtually any foundry can be used  $\rightarrow$  can use the lowest cost transistor circuits (big advantage)

- \* Adv.: topography after circuit fabrication is quite small, especially given the use of CMP to planarize the metallization layers

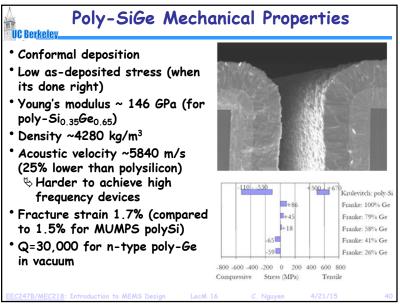

- \* Issue: limited thermal budget ⇒ limits the set of usable structural materials

- ♦ Metallization goes bad if temperature gets too high

- ♦ Aluminum grows hillocks and spikes junctions if T>500°C

- Scopper diffusion can be an issue at high temperature

- ♦ Low-k dielectrics used around metals may soon lower the temperature ceiling to only 320°C

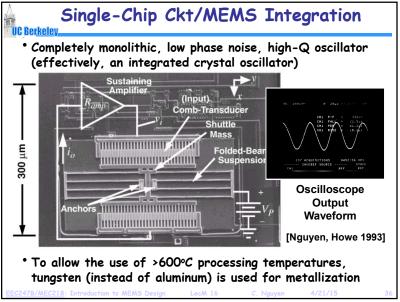

36

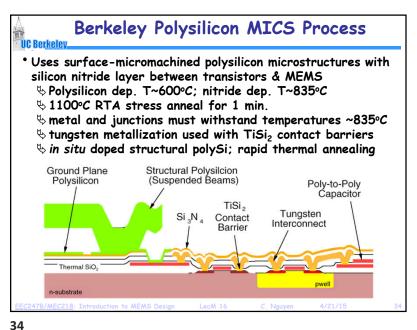

Usable MEMS-Last Integration Problem: tungsten is not an accepted primary interconnect <u>Challenge</u>: retain conventional metallization wminimize post-CMOS processing temperatures be explore alternative structural materials (e.g., plated nickel, SiGe [Franke, Howe et al, MEMS'99])  $\$  Limited set of usable structural materials  $\rightarrow$  not the best situation, but workable Barrier Interconnect Micromechanical (e.g., PECVD nitride) (e.g., polysilicon, nickel, etc.) Resonator Circuit Metal (e.g., polysilicon, nickel, etc. Circuit Interconnect Silicon Substrate

40

42

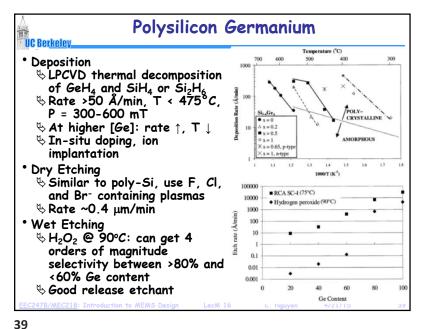

• 2 µm standard CMOS process w/ Al metallization • P-type poly-Si<sub>0.35</sub>Ge<sub>0.65</sub> structural material; poly-Ge sacrificial material • Process: ♦ Passivate CMOS w/ LTO @ 400°C ♥ Open vias to interconnect runners ♦ Deposit & pattern ground plane **Transistor** \$RTA anneal to lower resistivity (550°C, 30s) Circuits p+ Poly-SiGe p+ Poly-SiGe SiO. p+ Poly-Si N Substrate 41

IIC Berkeley

ASIMPS Ckt/MEMS Integration Process IIC Berkeley MEMS constructed from metal/insulator laminates of foundry CMOS Top metal layer used as etch mask for CHF<sub>3</sub>/O<sub>2</sub> metal-2 oxide etch metal-1 • Structures released via a movable microstructur final SF<sub>6</sub> isotropic dry etch • Independent electrostatic anchored actuation possible due to multiple insulated metal layers Metal/insulator Stress issues can be tricky stack ♦ Must design defensively against warping [G. Fedder, CMU]

ASIMPS Ckt/MEMS Integration Process IIC Berkeley \* Direct integration of Al/oxide MEMS structure with silicon CMOS or SiGe BiCMOS circuits Multiple electrodes within structures Derivatives for bulk silicon structures Composite Beam Gyro Resonator CMOS Transistor ใ Stator **Electrodes** Etched Pit | Silicon Substrate Uncooled IR [G. Fedder, CMU] **Detector Element**

UCB Poly-SiGe MICS Process

44