# EE C247B - ME C218 Introduction to MEMS Design Spring 2020

Prof. Clark T.-C. Nguyen

Dept. of Electrical Engineering & Computer Sciences

University of California at Berkeley

Berkeley, CA 94720

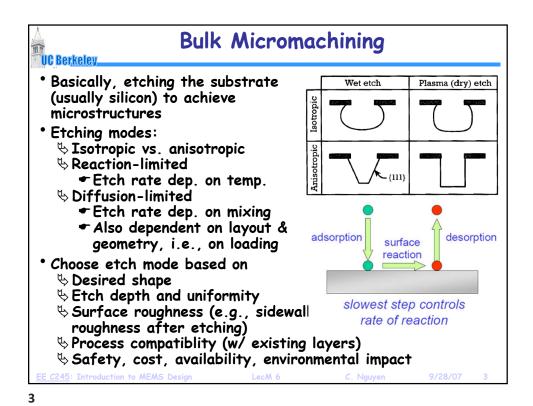

Lecture Module 6: Bulk Micromachining

EE C245: Introduction to MEMS Design

LecM 6

C Nauve

9/28/07

1

### IIC Rerkeley

#### Lecture Outline

- Reading: Senturia Chpt. 3, Jaeger Chpt. 11, Handouts:

"Bulk Micromachining of Silicon"

- Lecture Topics:

- Sulk Micromachining

- Shanisotropic Etching of Silicon

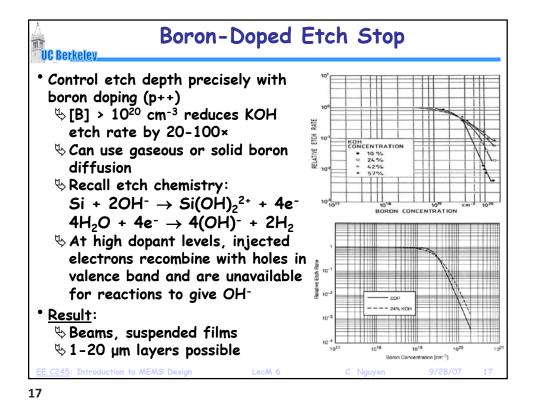

- **⇔** Boron-Doped Etch Stop

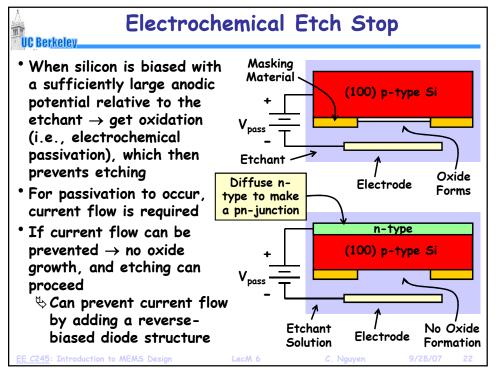

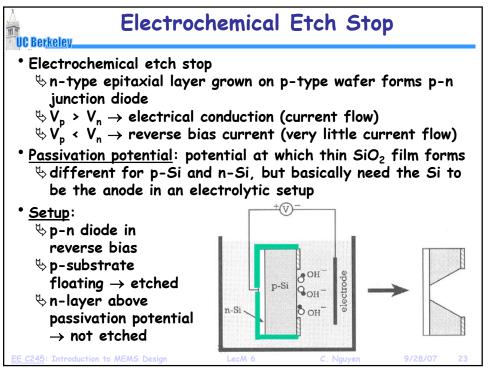

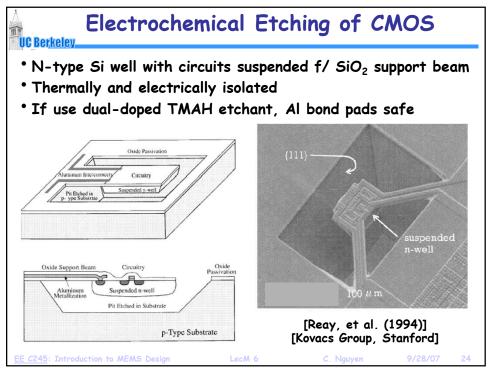

- \$ Electrochemical Etch Stop

- **♥ Isotropic Etching of Silicon**

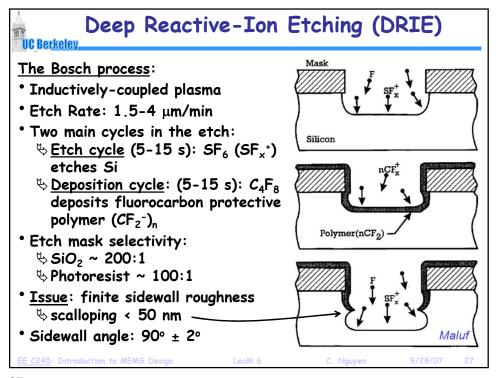

- ♦ Deep Reactive Ion Etching (DRIE)

- ♥ Wafer Bonding

E C245: Introduction to MEMS Design

LecM 6

C. Nguyen

9/28/07

Mechanical Properties of Silicon

UC Berkeley

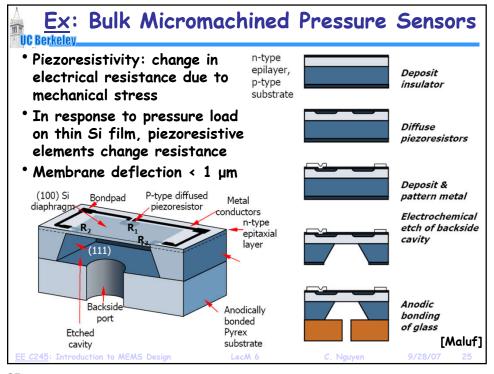

Crystalline silicon is a hard and brittle material that deforms elastically until it reaches its yield strength, at which point it breaks.

Tensile yield strength = 7 GPa (~1500 lb suspended from 1 mm²)

♦ Young's Modulus near that of stainless steel

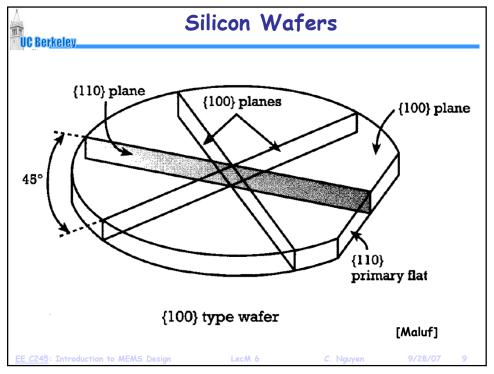

∜{100} = 130 GPa; {110} = 169 GPa; {111} = 188 GPa

Mechanical properties uniform, no intrinsic stress

♦ Mechanical integrity up to 500°C

Good thermal conductor

**♦Low** thermal expansion coefficient

\$ High piezoresistivity

EE C245: Introduction to MEMS Design

LecM 6

C. Nguyen

9/28/07

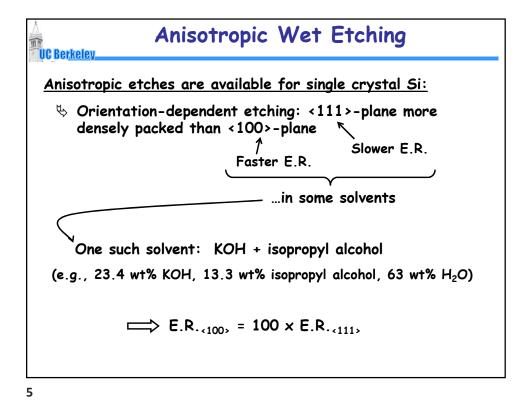

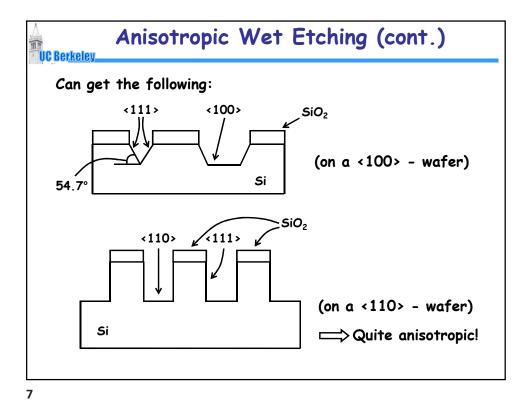

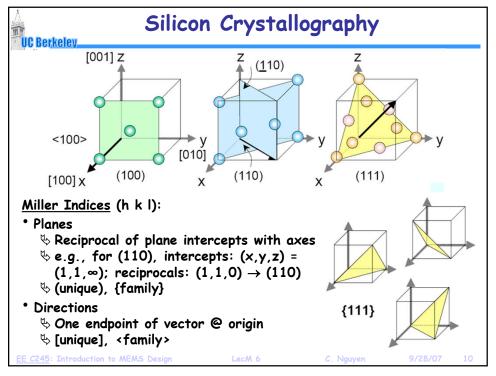

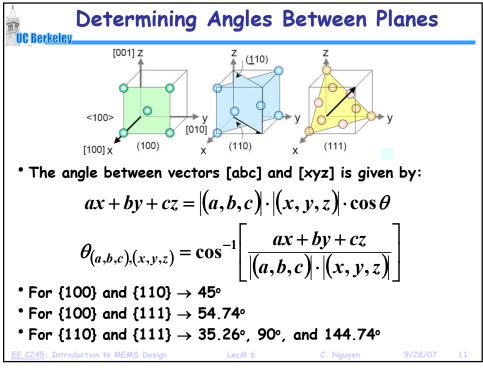

Anisotropic Etching of Silicon UC Berkeley Etching of Si w/ KOH Self-limiting etches  $Si + 2OH^- \rightarrow Si(OH)_2^{2+} + 4e^ 4H_2O + 4e^- \rightarrow 4(OH)^- + 2H_2$  Crystal orientation dependent etch rates below the surface & 2 dangling bonds that can react  $\P$  {111} plane has three of its bonds below the surface & Front side mask {100} only one dangling bond to react  $\rightarrow$  much slower E.R. ⟨⟨§ {111⟩ forms protective oxide | ⟨⟨ 111⟩ smoother than other crystal planes  $\rightarrow$  good for Back side mask optical MEMS (mirrors)

Anisotropic Etching of Silicon UC Berkeley. **Photoresist**  Deposit nitride: Nitride Mask ★ Target = 100nm \$ 22 min. LPCVD @800°C • Lithography to define areas of silicon to be etched Etch/pattern nitride mask RIE using SF6 Silicon Substrate ♦ Remove PR in PRS2000 Etch the silicon

Use 1:2 KOH:H<sub>2</sub>O (wt.), stirred bath @ 80°C **Opening to Silicon** ♥ Etch Rates: • (100) Si  $\rightarrow$  1.4 µm/min • Si<sub>3</sub>N<sub>4</sub>  $\rightarrow$  ~ 0 nm/min • SiO<sub>2</sub>  $\rightarrow$  1-10 nm/min Silicon Substrate Photoresist, Al → fast Micromasking by H<sub>2</sub> bubbles leads to roughness

Stir well to displace bubbles (100) Can also use oxidizer for (111) surfaces > Or surfactant additives to Silicon Substrate suppress bubble formation

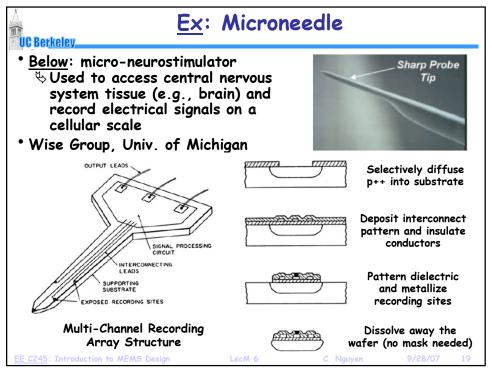

• Micronozzle using anisotropic etch-based fabrication

• Used for inkjet printer heads

Resist p++ silicon

1. Pattern mask

2. Etch circle in p++

3. Mask front side

4. Anisotropic etch

[Maluf]

## Recipe-Based Suppression of "Footing"

- Use higher process pressure to reduce ion charging [Nozawa]

- $\heartsuit$  High operating pressure  $\rightarrow$  concentration of (-) charge increases and can neutralize (+) surface charge

- ➡ <u>Issue</u>: must introduce as a separate recipe when the etch reaches the Si-insulator interface, so must be able to very accurately predict the time needed for etching

- Adjust etch recipe to reduce overetching [Schmidt]

- $\$  Change  $C_4F_8$  flow rate, pressure, etc., to enhance passivation and reduce overetching

- ➡ <u>Issue</u>: Difficult to simultaneously control footing in a narrow trench and prevent grass in wide trenches

- Use lower frequency plasma to avoid surface charging [Morioka]

- $\$  Low frequency  $\rightarrow$  more ions with low directionality and kinetic energy  $\rightarrow$  neutralizes (-) potential barrier at trench entrance

- ♦ Allows e<sup>-'</sup>s to reach the trench base and neutralize (+) charge → maintain charge balance inside the trench

EE C245: Introduction to MEMS Design

ecM 6

9/28/07

9/28/07 30

#### Metal Layer Bonding UC Berkeley\_

- Pattern seal rings and bond pads photolithographically

- Eutectic bonding

- Uses eutectic point in metal-Si phase diagrams to form silicides

- ♦ Au and Si have eutectic point at 363°C

- ♦ Low temperature process

- ♦ Can bond slightly rough surfaces

♦ Issue: Au contamination of CMOS

- Solder bonding

- ♦ PbSn (183°C), AuSn (280°C)

♦ Lower-T process

- Scan bond very rough surfaces

- ♦ <u>Issue</u>: outgassing (not good for encapsulation)

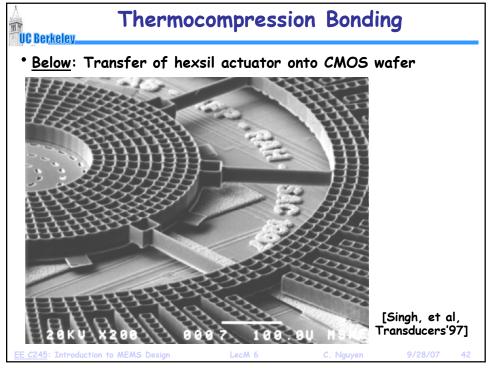

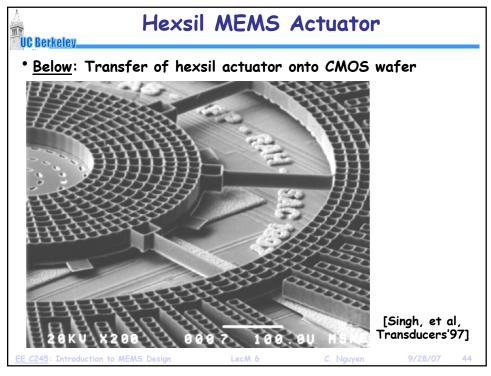

- Thermocompression

- Scommonly done with electroplated Au or other soft metals

- ♦ Room temperature to 300°C

- \$Lowest-T process

- Scan bond rough surfaces with topography

41