1

Spanos & Poolla

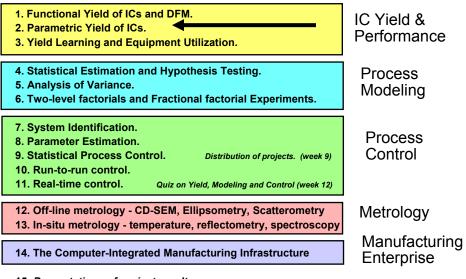

#### Fall 2003 EE290H Tentative Weekly Schedule

15. Presentations of project results.

Lecture 2: Parametric Yield

EE290H F03

# IC Yield and Performance (cont.)

- Defect Limited Yield

- · Definition and Importance

- Metrology

- Modeling and Simulation

- Design Rules and Redundancy

- Parametric Yield

- Parametric Variance and Profit

- Metrology and Test Patterns

- Modeling and Simulation

- Worst Case Files and DFM

- Equipment Utilization

- Definition and NTRS Goals

- · Measurement and Modeling

- Industrial Data

- · General Yield Issues

- Yield Learning

- · Short loop methods and the promise of in-situ metrology

Lecture 2: Parametric Yield

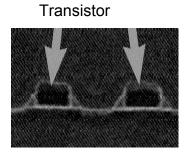

# IC Structures can be highly Variable

Interconnect

#### Variability will impact performance

Lecture 2: Parametric Yield

EE290H F03

Spanos & Poolla

3

# What is Parametric Yield?

- When devices (transistors) do not have the exact size they were designed for,

- when interconnect (wiring) does not have the exact values (Ohms/µm, Farads/µm2, etc.) that the designer expected,

- when various structures (diffused layers, contact holes and vias, etc.) are not exactly right,

- the circuit may work, but

- performance (speed, power consumption, gain, common mode rejection, etc.) will be subject to statistical behavior...

5

Spanos & Poolla

#### What are the Parametric Yield Issues?

- Binning and Impact on Profitability

- The <u>Process</u> and <u>Performance</u> Domains

- Characterizing the Process Domain

- Identifying Critical Variables

- Modeling Process Variability

- Associated (Statistical) Metrology

- · Process Variability and the Circuit Designer

- Design for Manufacturability Methods

- A Global (re)view of Yield

Lecture 2: Parametric Yield

EE290H F03

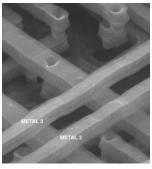

What is *the* Critical Dimension?

#### Gate is typically made out of Polysilicon

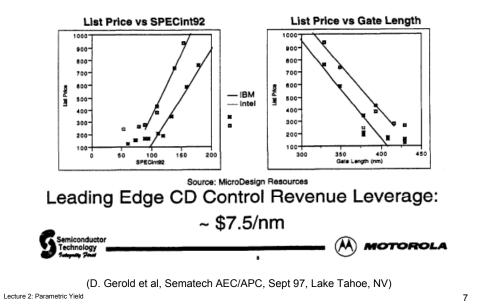

# **Basic CD Economics**

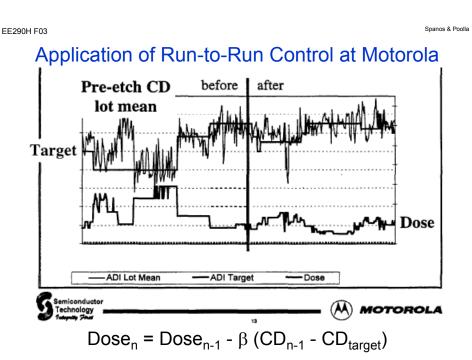

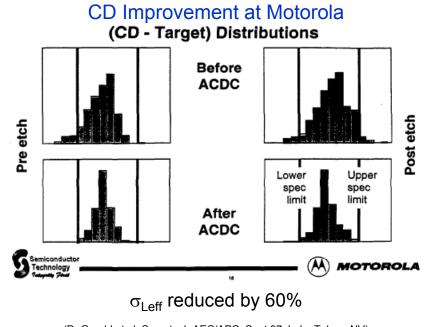

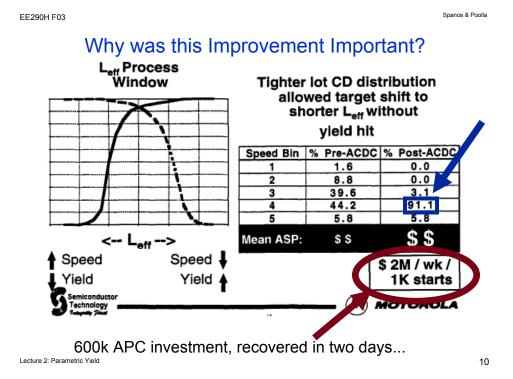

Lecture 2: Parametric Yield (D. Gerold et al, Sematech AEC/APC, Sept 97, Lake Tahoe, NV)

8

Lecture 2: Parametric Yield (D. Gerold et al, Sematech AEC/APC, Sept 97, Lake Tahoe, NV)

9

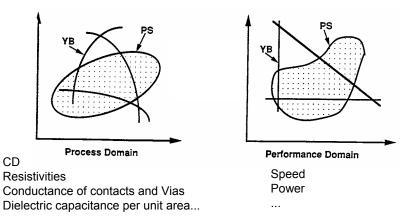

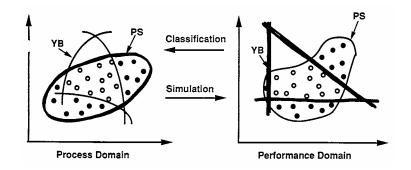

#### **Process and Performance Domains**

- · CD is not the only process variable of interest...

- · Speed is not the only performance of interest...

- In general we have a mapping between two multidimensional spaces:

Lecture 2: Parametric Yield

EE290H F03

Spanos & Poolla

11

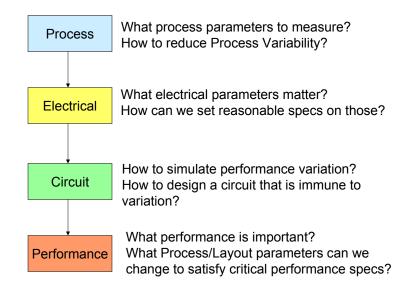

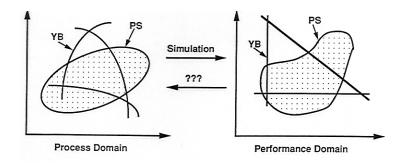

#### So, what to do?

#### Translating Specifications between Domains

- Performance Specs, imposed by the market, translate to an "acceptability region" in the process domain.

- This "acceptability region" is also known as the Yield Body (YB).

- The Yield Body can be mapped into either domain.

Lecture 2: Parametric Yield

EE290H F03

Spanos & Poolla

13

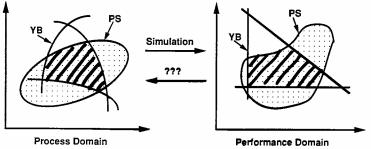

#### So what is Parametric Yield?

- One is interested in *mapping* and in *maximizing* the overlap between YB and PS.

- This can be accomplished in various ways.

- first, we should be able to <u>measure</u> (characterize) the Process Spread (PS).

- · then, one has to figure the mapping from Process to Performance!

- · Finally, one needs design tools to manipulate the above.

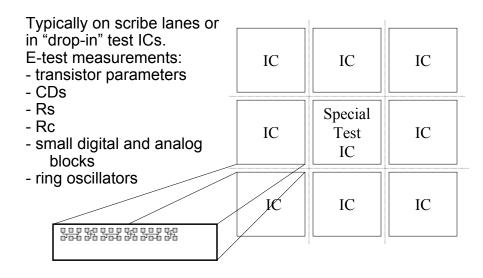

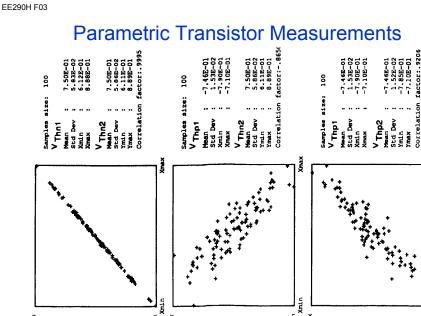

# **Parametric Test Patterns**

Lecture 2: Parametric Yield

15

Spanos & Poolla

X

Ymin

Ymax X

Ymax Ymax

Lecture 2: Parametric Yield

rmax

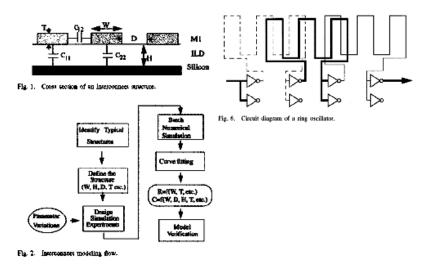

An Extraction Method to Determine Interconnect Parasitic Parameters, C-J Chao, S-C Wong, M-J Chen, B-K Liew, IEEE TSM, Vol 11, No 4. Nov 1998.

Lecture 2: Parametric Yield

17

Spanos & Poolla

EE290H F03

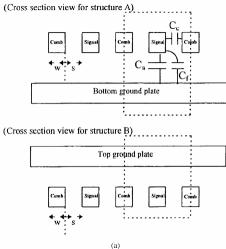

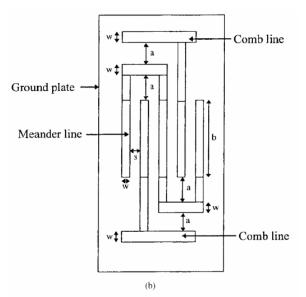

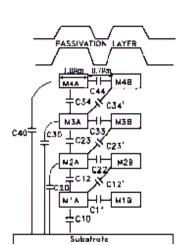

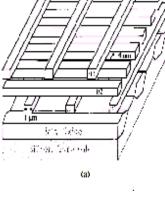

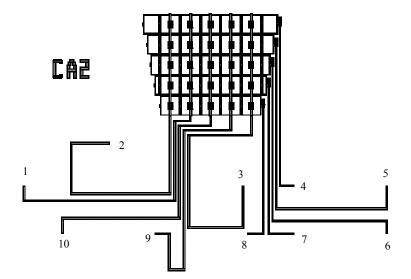

# Interconnect Characterization Structures

Fig. 1. Top view and cross section of interconnect parasitic test structure.

EE290H F03

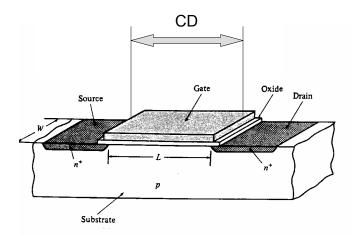

Interconnect Structures are very Complex...

EE290H F03

Spanos & Poolla

Spanos & Poolla

21

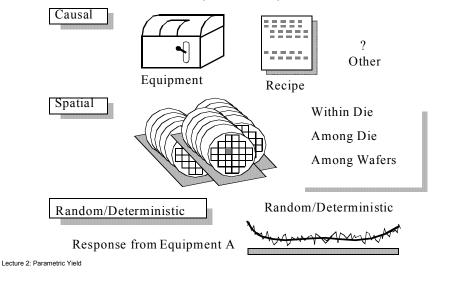

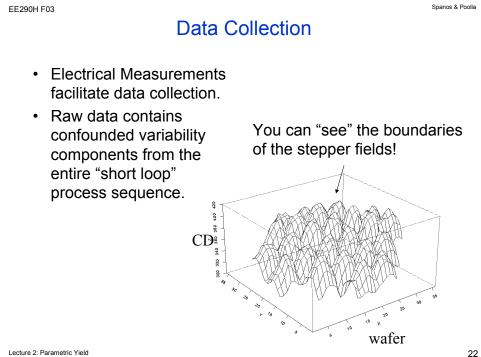

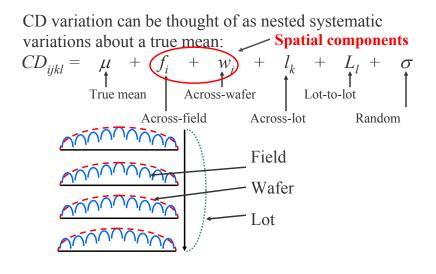

# Statistical Metrology for CDs

Where does variability come from? What are its spatial components?

#### Nested Variance – A Simple Model

Lecture 2: Parametric Yield

Jason Cain, SPIE 2003 23

Spanos & Poolla

EE290H F03

Experimental Design

- Use a mask with densely grouped test features to explore spatial variability.

- Electrical linewidth metrology (ELM) chosen as primary metrology due to its high speed.

- A fabrication process based on a standard 248 nm lithography process was used to print test wafers.

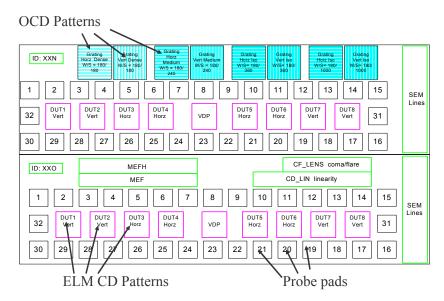

#### **Test Mask Design**

- Mask design consists of a 22x14 array of test modules

- Module has CD structures (ELM, CD-SEM, OCD) in varying pitch, orientation, and OPC use.

- Density of structures allows detailed variance maps using an "exhaustive" sampling plan.

- Three feature types measured for each module for every field on the wafer (all no-OPC).

Lecture 2: Parametric Yield

EE290H F03

Lecture 2: Parametric Yield

Spanos & Poolla

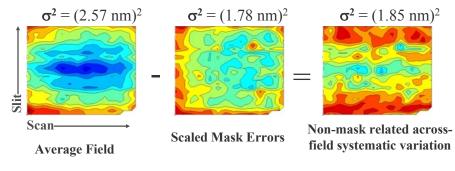

# Across-Field Systematic Variation – Mask Errors

Calculate average field to see across-field systematic variation

Use mask measurements to decouple scaled mask errors from non-mask related systematic variation

Lecture 2: Parametric Yield

27

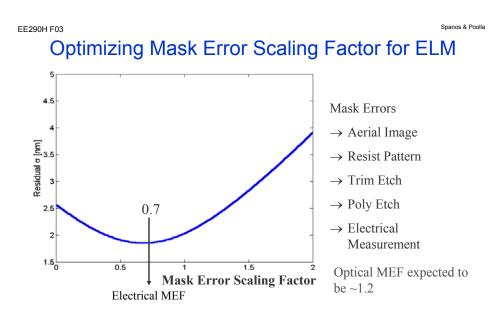

Mask error scaling factor optimized to minimize residuals when mask errors are removed from average field.

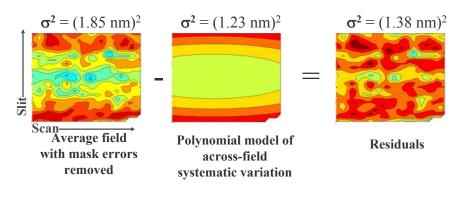

#### Across-Field Systematic Variation

Polynomial model used to capture across-field systematic variation (inferred from examination of data):

$$CD(X_f, Y_f) = aX_f^2 + bY_f^2 + cX_f + dY_f$$

Lecture 2: Parametric Yield

29

#### EE290H F03

Spanos & Poolla

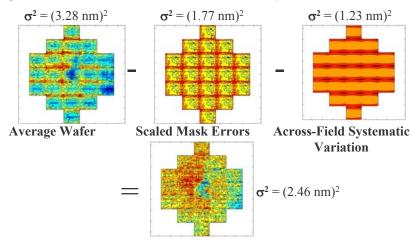

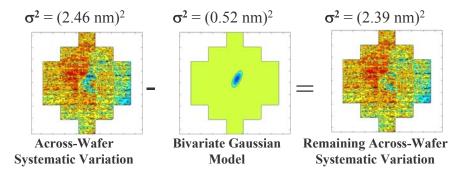

### Across-Wafer Systematic Variation

Separation of Across-Field and Across-Wafer Systematic Variation:

**Across-Wafer Systematic Variation**

#### Across-Wafer Systematic Variation

- There is a distinct local drop in CD value in the wafer center, most likely linked to the way the develop fluid is dispensed.

- A bivariate Gaussian function was fitted to the data to remove this effect.

Lecture 2: Parametric Yield

31

EE290H F03

Spanos & Poolla

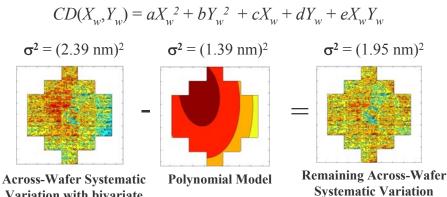

#### Across-Wafer Systematic Variation

The remaining across-wafer systematic variation was removed using a polynomial model:

Across-Wafer Systematic Variation with bivariate Gaussian removed

Lecture 2: Parametric Yield

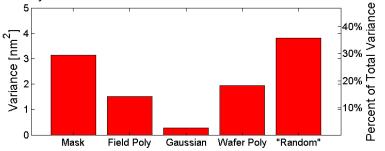

#### Systematic Variation Model Summary

- Across-field systematic variation:

- Mask errors (magnified scaling factor) removed

- Polynomial terms in X and Y across the field

- Across-wafer systematic variation:

- Across-field systematic variation removed

- Bivariate Gaussian for spot effect (likely linked to develop effect)

- Polynomial terms in X and Y across the wafer

Lecture 2: Parametric Yield

EE290H F03

33

Spanos & Poolla

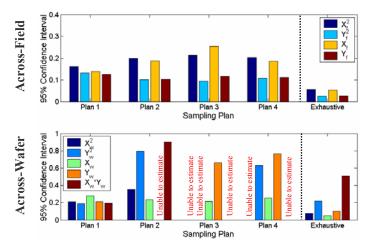

# **Reduced Sampling Plan Candidates**

Each plan requires roughly one hour of measurement time (Exhaustive plan had 21,252 measurements, requiring 25 hours)

### **Comparison of Reduced Sampling Plans**

Plan 1 offers the best estimate of across-wafer variation without compromising the quality of the across-field estimate.

Lecture 2: Parametric Yield

35

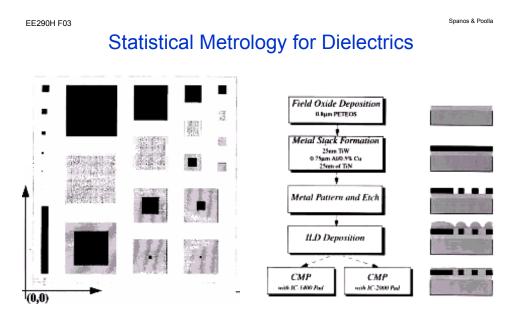

Rapid Characterization and Modeling of Pattern-Dependent Variation in Chemical-Mechanical Polishing Brian E. Stine, Dennis O. Ouma, *Member, IEEE*, Rajesh R. Divecha, *Member, IEEE*, Duane S. Boning, *Member, IEEE*, James E. Chung, *Member, IEEE*, Dale L. Hetherington, *Member, IEEE*, C. Randy Harwood, O. Samuel Nakagawa, and Soo-Young Oh, *Member, IEEE*, IEEE TSM, VOL. 11, NO. 1, FEBRUARY 1998 Lecture 2: Parametric Yield 36

# Dielectric Thickness vs Position in Field

Studies like this can be used to complement "random" variability with the deterministic, pattern dependent variability.

The combination of the two leads to simulation tools that can predict very well the "spread" of circuit performances.

37

EE290H F03

Spanos & Poolla

# Impact of Process Variability to Circuit Performance

- Obviously, not everything in the process impacts the Circuit Performance.

- Studies have tried to focus on the most important process parameters.

- CD is clearly one of them.

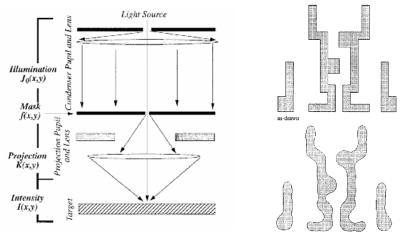

# Impact of Pattern-Dependent Poly-CD Variation

#### Use basic Optical Model to determine "actual" pattern...

aerial imaged ("as-manufactured")

Simulating the Impact of Pattern-Dependent Poly-CD Variation on Circuit Performance, Stine, et al, IEEE TSM, Vol 11, No 4, November 1998 Lecture 2: Parametric Yield

39

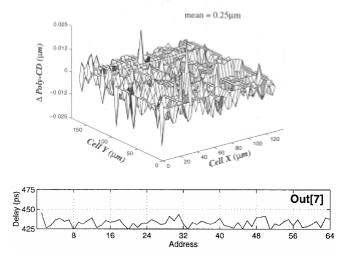

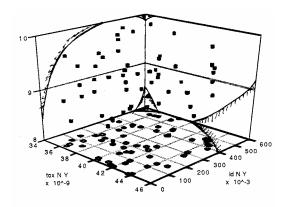

# EE290H F03 Simulated Performance Variability in 64x8 SRAM Macrocell

#### Simulated Die (Cell) Level Variation

Lecture 2: Parametric Yield

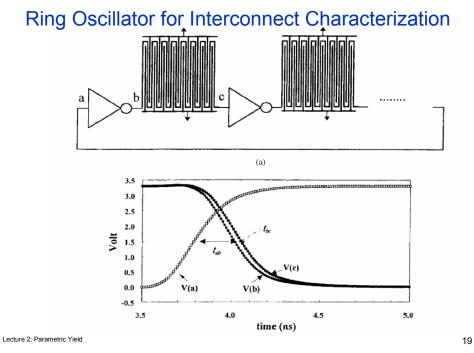

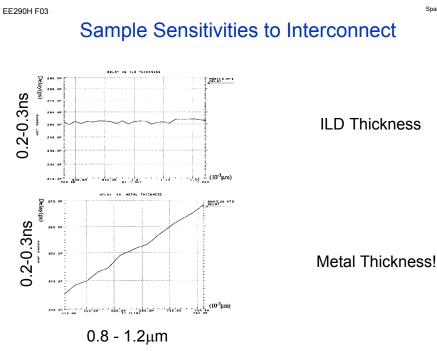

# Circuit Sensitivity to Interconnect Variation

Circuit Sensitivity to Interconnect Variation, Lin, Spanos and Milor, IEEE TSM, Vol 11, No 4, November 1998

Lecture 2: Parametric Yield

41

Spanos & Poolla

Lecture 2: Parametric Yield

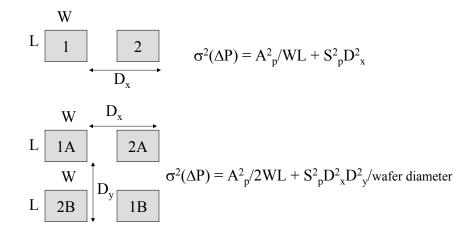

#### Modeling Spatial Matching

- Component Matching is an aspect of process variability that affects the yield of Analog Circuits:

- D-A converters: capacitor matching.

- Diff amplifiers, current sources: transistor matching.

Lecture 2: Parametric Yield

EE290H F03

43

Spanos & Poolla

#### **Circuit Element "Matching" Models**

- In order to describe matching one needs a "spatial" distribution.

- In this case *location*, as well as *distance* are factors that will affect process (and performance) variability.

- Several models have been created, either empirically, or by taking into account detailed device parameters.

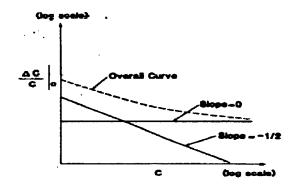

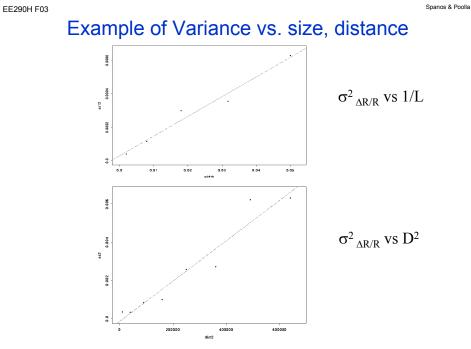

# Pelgrom's Model

Variance inversely proportional to area, proportional to distance<sup>2</sup>.

Lecture 2: Parametric Yield

45

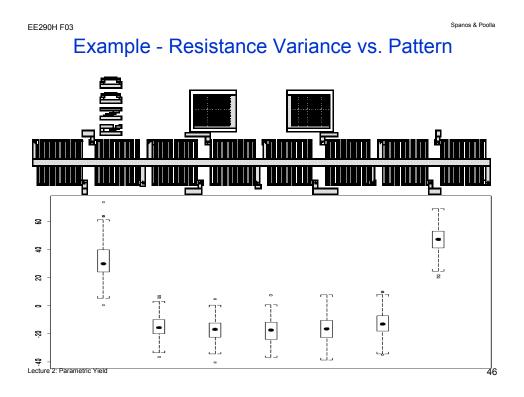

# Example on Variance in Element Array

Lecture 2: Parametric Yield

47

#### Simulating Parametric Yield

- The process domain can be mapped to the performance domain through random exploration.

- The Yield can then be estimated as Y= Np/N.

- Though this estimate converges rather slowly, it does have some nice properties.

Lecture 2: Parametric Yield

EE290H F03

49

Spanos & Poolla

# Monte Carlo - the speed of Convergence

• Since Y is an estimate of a random variable, bounds for the actual value of Y are given by the general Tchebycheff inequality:

• Since each random experiment can be seen as a Bernoulli trial with Y probability of success, then if N is large and Y(1-Y)N>6 (or so), we can employ the approximation:

$$\mu_{Y} = Y$$

• The estimation accuracy is <u>independent of the</u> dimensionality of the process domain.

definitions: Y: actual yield, N: number of Monte Carlo trials,  $\mu_{\text{Y}},\,\sigma^2_{\text{Y}}$  are the mean and variance of the estimated yield  $\text{Y}_{est}.$

Spanos & Poolla

Lecture 2: Parametric Yield

EE290H F03

51

Spanos & Poolla

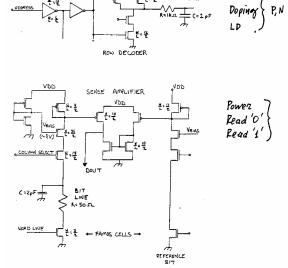

# The two Domains for the Sense Amp

Lecture 2: Parametric Yield

# Yield Simulation Example

N = 100, Np = 59 Y = 0.59,  $\sigma_y^2 = Y(1-Y)/N = 0.05^2$ Y = 0.59 +/-0.15 =>  $0.44 \le Y \le 0.74$

Lecture 2: Parametric Yield

EE290H F03

# Next Time on Parametric Yield

- Current and Advanced DFM techniques

- The role of process simulation (TCAD)

- Complete Process Characterization

- Worst Case Files

- Statistical Design

- · The economics of DFM

53

Spanos & Poolla