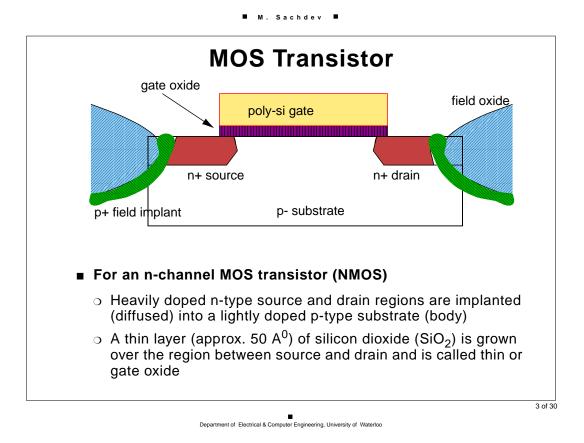

# M. Sachder MCOSFET: Introduction Metal oxide semiconductor field effect transistor (MOSFET) or MOS is widely used for implementing digital designs Its major assets are: Higher integration density, and Relatively simple manufacturing process As a consequence, it is possible to realize 10<sup>6-7</sup> transistors on an integrated circuit (IC) economically

📕 M. Sachdev 🔳

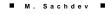

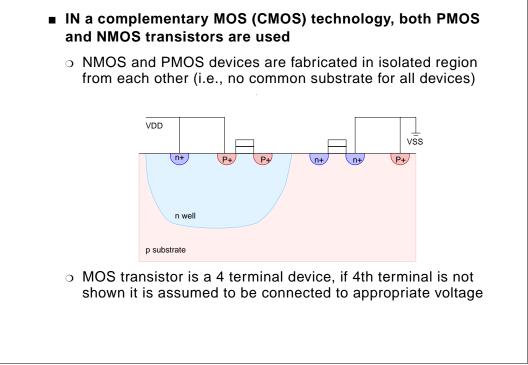

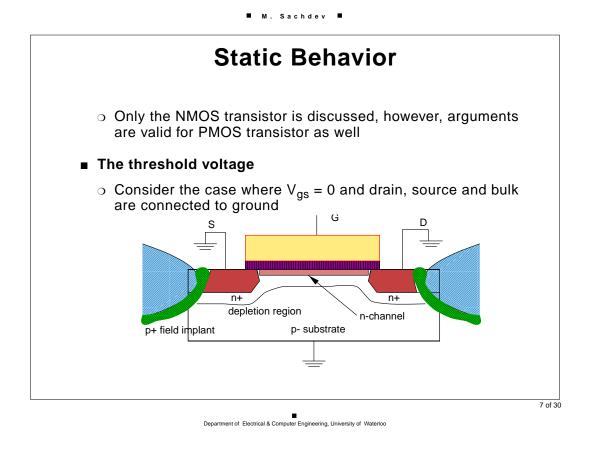

- A technology that uses NMOS (PMOS) transistors only is called NMOS (PMOS) technology

- In NMOS or PMOS technologies, substrate is common and is connected to +ve voltage, VDD (NMOS) or GND (PMOS)

5 of 30

### ■ M. Sachdev ■

### 📕 M. Sachdev 📕

- Further V<sub>GS</sub> increase does not increase the depletion width but increases electrons in the inversion layer

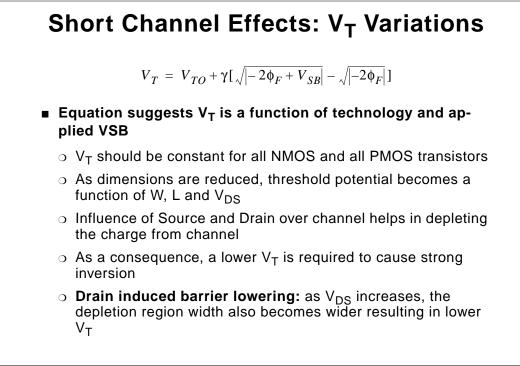

- Threshold Voltage

$$V_T = V_{TO} + \gamma \left[ \sqrt{\left| -2\phi_F + V_{SB} \right|} - \sqrt{\left| -2\phi_F \right|} \right]$$

$\circ$  Where

0

$$\gamma = \frac{\sqrt{2q\varepsilon_{si}N_A}}{C_{ox}}$$

$\odot~V_{T}$  is +ve for NMOS and -ve for PMOS devices

9 of 30

Department of Electrical & Computer Engineering, University of Waterloo

M. Sachdev 🔳

11 of 30

Department of Electrical & Computer Engineering, University of Waterloo

### 📕 M. Sachdev 📕

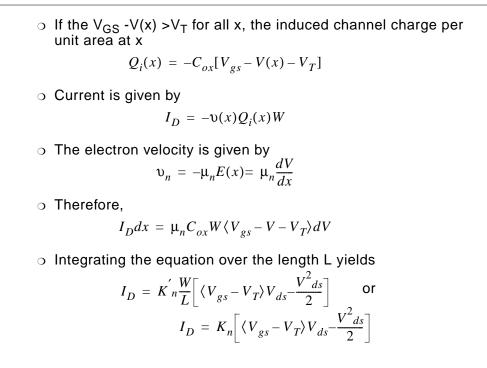

$\circ\,$  k'\_n is known as the process trans-conductance parameter and equals

$$K'_n = \mu_n C_{ox} = \mu_n \frac{\varepsilon_{ox}}{t_{ox}}$$

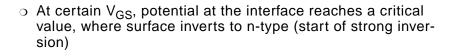

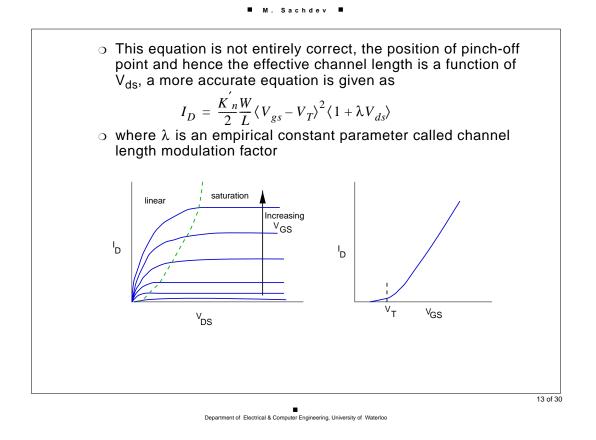

- If the V<sub>GS</sub> is further increased, then at some x, V<sub>GS</sub> V(x) <V<sub>T</sub> and that point the channel disappears and transistor is said to be pinched-off

- $\odot\,$  Close to drain no channel exists, the pinched-off condition in the vicinity of drain is V\_{GS} V\_{DS} <=V\_{T}

- o Under these conditions, transistor is in the saturation region

- If a complete channel exists between source and drain, then transistors is said to be in triode or linear region

- $\circ$  Replacing V<sub>DS</sub> by V<sub>GS</sub> -V<sub>T</sub> in the current equation we get, MOS current-voltage relationship in saturation region

$$I_D = \frac{K_n W}{2} \langle V_{gs} - V_T \rangle^2$$

### 📕 M. Sachdev 📕

15 of 30

Department of Electrical & Computer Engineering, University of Waterloo

### 📕 M. Sachdev 📕

Department of Electrical & Computer Engineering, University of Waterloo

### M. Sachdev

Department of Electrical & Computer Engineering, University of Waterloo

M. Sachdev

19 of 30

Department of Electrical & Computer Engineering, University of Waterloo

## M. Sachdev **I**

20 of 30

Department of Electrical & Computer Engineering, University of Waterloo

# Sub-threshold Conduction

M. Sachdev

MOS transistor partially conducts for V<sub>gs</sub> <V<sub>T</sub>

- Known as sub-threshold conduction or weak-inversion conduction

- Very small for long-channel (10<sup>-12</sup>A/micron)

- $\odot\,$  The inverse rate of decrease in current with respect to  $V_{gs}$  is given by

$$S = \left(\frac{d}{dV_{gs}}\ln(I_D)\right)^{-1} = \frac{kT}{q}\ln 10(1+\alpha)$$

$\circ \frac{kT}{2} \ln 10 = 60 \text{ mV/decade and } \alpha$  is 0 for an ideal transistor

$\circ$  However, $\alpha$  is greater than 1 for real transistor making S = 80 mV/decade

Department of Electrical & Computer Engineering, University of Waterloo

26 of 30

### Several MOS models have been developed

- Model complexity is a trade-off between accuracy and run time in simulator

- In SPICE, model complexity is set by LEVEL parameter

- Level 1: spice model is based on long channel MOS I-V equation; no longer used

- Level 2: geometry, physics based; uses several short channel effects; complex and inaccurate; no longer used

- Level 3: semi-empirical model

- Level 4: empirical model based on extracted values from experimental data; widely used

- Several other models are available; virtually every semiconductor fab has some model development group

27 of 30

Department of Electrical & Computer Engineering, University of Waterloo

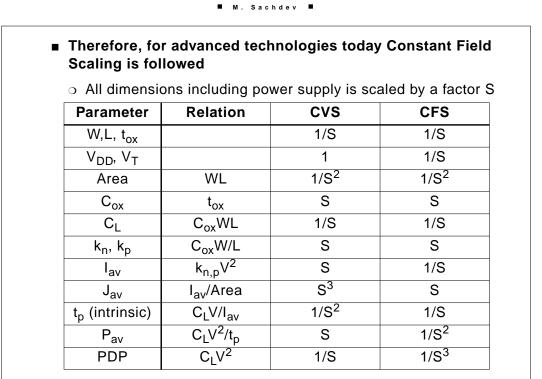

# **Technology Scaling & CMOS**

M. Sachdev 📕

- Ever since ICs were invented, dimensions are scaled to

- o Integrated more transistors in the same area

- Allow higher operational speed

Scaling has profound impact on many aspects of ICs

### Constant Voltage Scaling

- All device dimensions are scaled by a factor S

- $\circ$  Voltage (i.e., V<sub>DD</sub>) after the scaling is same as before

- o This method of scaling is followed till 0.8 micron

- However for lower geometries, higher electric field resulted in poor device reliability

29 of 30

Department of Electrical & Computer Engineering, University of Waterloo