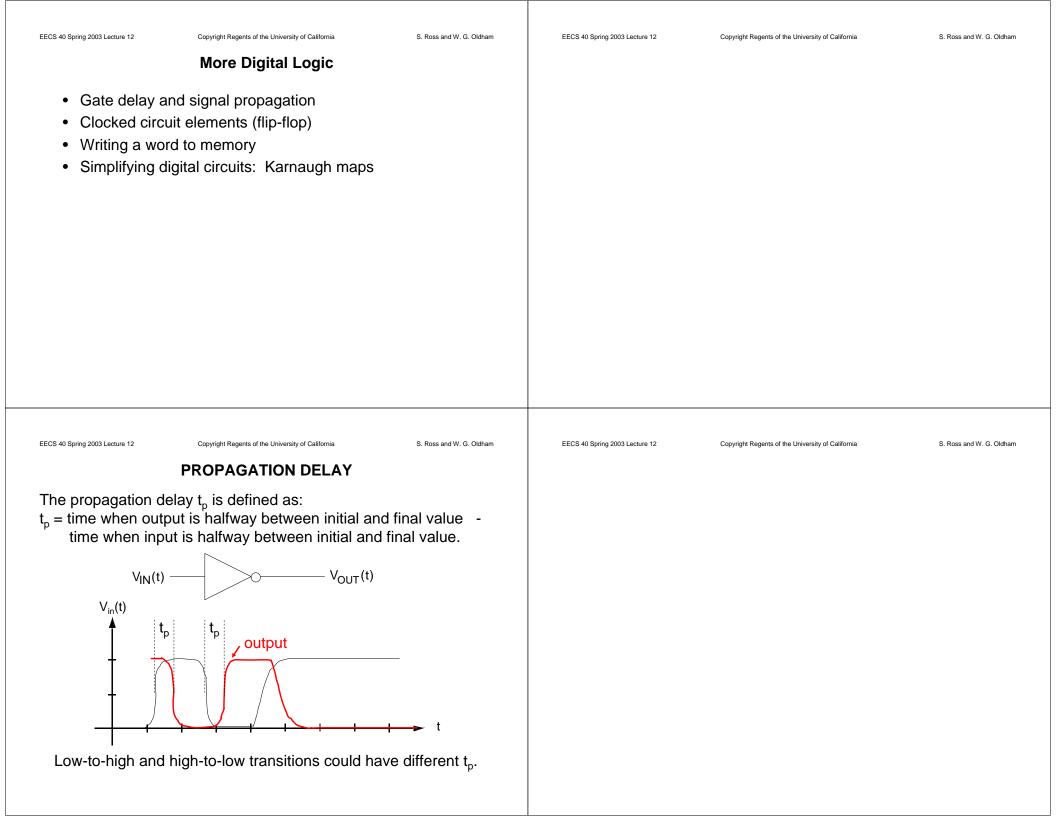

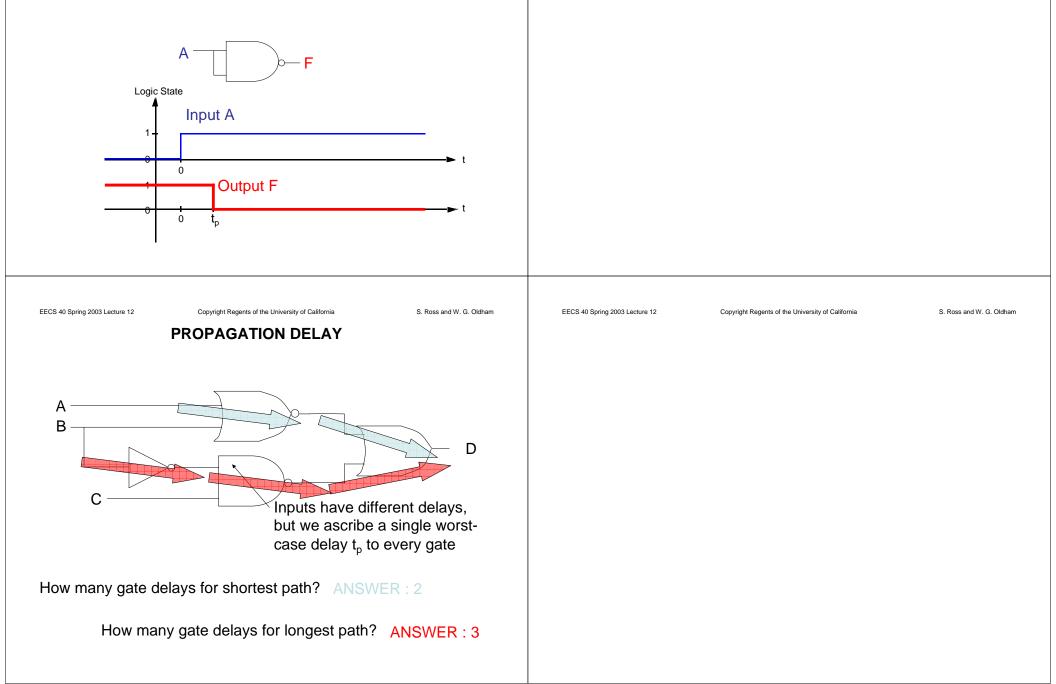

#### PROPAGATION DELAY

To get an approximate idea of the effects of delay, we make the transitions look instantaneous (though they are exponential).

S. Ross and W. G. Oldham

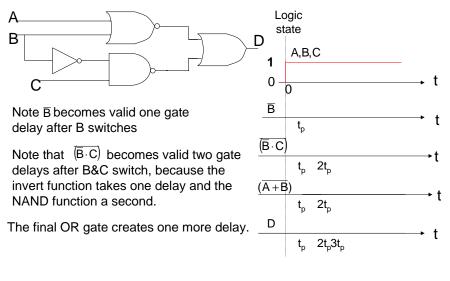

### TIMING DIAGRAMS

Different delays through different paths can create "false" output: Circuit computes using partially updated signals.

EECS 40 Spring 2003 Lecture 12

Copyright Regents of the University of California

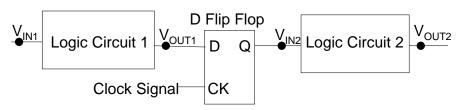

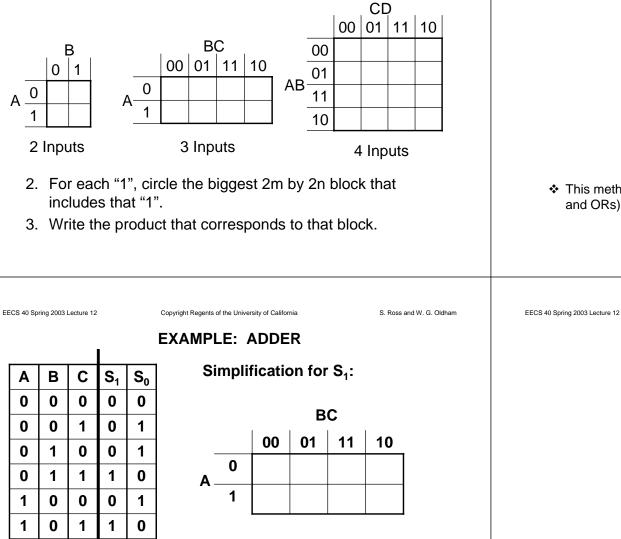

#### SYNCHRONOUS LOGIC

We have now seen that a circuit can produce nonsensical output due to differing delay paths in the circuit.

Presumably, the output of a logic circuit might serve as the input of a second logic circuit.

How do we prevent the second circuit from using and passing on this false information?

Answer: Include "gatekeeper" components that pass on data only when enough time has passed to guarantee validity

Clocked (Synchronous) components: flip-flops

EECS 40 Spring 2003 Lecture 12

Copyright Regents of the University of California

S. Ross and W. G. Oldham

S. Ross and W. G. Oldham

EECS 40 Spring 2003 Lecture 12

Copyright Regents of the University of California

S. Ross and W. G. Oldham

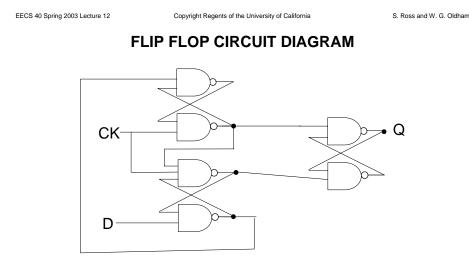

# SYNCHRONOUS CIRCUIT

The D Flip Flop is a synchronous (clocked) sequential (memory) circuit.

At the instant the clock signal CK rises from logic 0 to logic 1, the output Q is set equal to the input D.

At all other times, the output Q remains the same.

The flip flop prevents Logic Circuit 2 from receiving a new input value, until the clock transition allows the data to pass through.

We may cover digital circuits with feedback later in the course.

1

1

1

1

Input

0

1

1

1

0

1

Output

S. Ross and W. G. Oldham

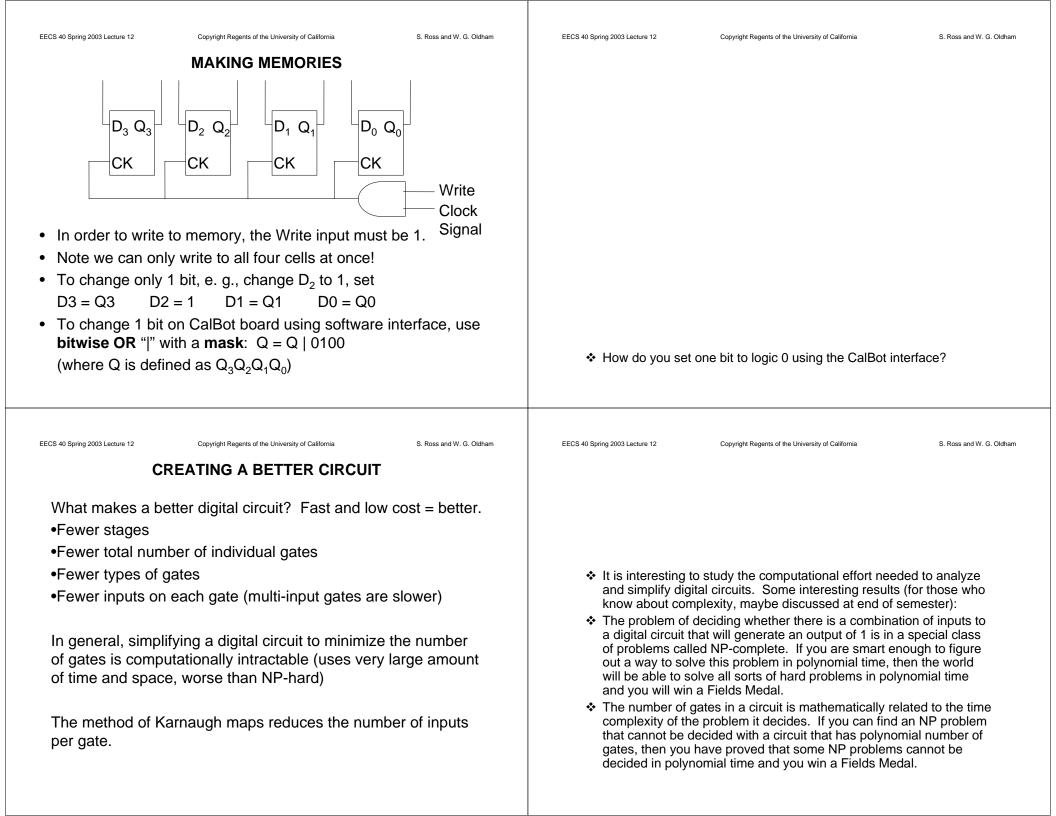

# **KARNAUGH MAPS**

To find a simpler sum-of-products expression,

1. Write the truth table of your circuit into a special table.

This method simplifies circuits to smaller sum-of-products (ANDs and ORs). Could you use these maps to simplify with XOR?

Copyright Regents of the University of California

| Use the Karnaugh map method to simplify S <sub>0</sub> . Is the circuit for S <sub>0</sub> ? | re a simpler |

|----------------------------------------------------------------------------------------------|--------------|

|----------------------------------------------------------------------------------------------|--------------|