## Final Exam May 18, 2004 Time Allowed: 3 Hours

Solutions

| Name:               |              |

|---------------------|--------------|

| Last                | First        |

| Student ID #:       | , Signature: |

| Discussion Section: |              |

This is a closed-book exam, except for use of three 8.5 x 11 inch sheets of your notes. Show all your work to receive full or partial credit. Write your answers clearly in the spaces provided.

Dennis Fack

Mervin

Siddherk

Arko

Steve

Juck

| Problem #: | Points: |  |

|------------|---------|--|

| 1          | /10     |  |

| 2          | /10     |  |

| 3          | /10     |  |

| 4          | /15     |  |

| 5          | /10     |  |

| 6          | /10     |  |

| 7          | /15     |  |

| Total      | /80     |  |

#### 1. (10 points)

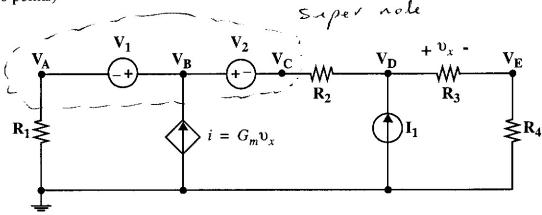

Figure 1

In the circuit of Figure 1, all voltage sources, current sources and resistors are known. Write a set of node equations sufficient to solve the circuit. You must use the labeled node potentials  $V_A$ ,  $V_B$ ,  $V_C$ ,  $V_D$  and  $V_E$ . Do <u>not</u> solve your equations.

$$\frac{V_A}{R_1} - G_m \left( V_D - V_E \right) + \frac{V_C - V_D}{R_2} = 0$$

$$V_A - V_C = -V_1 + V_2$$

$$\frac{V_0 - V_C}{R_2} + \frac{V_0 - V_E}{R_3} = I,$$

$$\frac{V_{E}-V_{P}}{R_{3}}+\frac{V_{E}}{R_{Y}}=0$$

4 eg's in 4 untenouns { Va, Vc, Va, VE }

IF

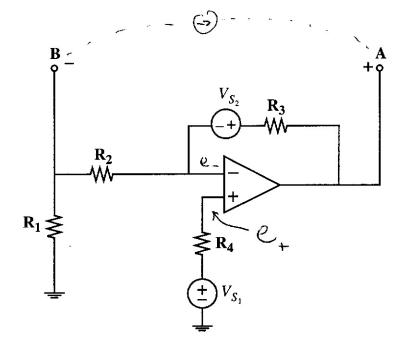

Figure 2

The op-amp in Figure 2 is ideal. Determine the Thevenin Equivalent Circuit with respect to the two terminals A and B.

(1)

$$V_{OC}$$

by superposition:  $V_{OC} = \frac{R_c + R_3}{R_1 + R_2} V_{S_1} + V_{S_2}$

$V_{S_1}$  only:  $C_{+} = C_{-} = V_{S_1}$

$V_{B} = \frac{R_1}{R_1 + R_2} V_{S_1}$

$V_{A} = \frac{R_2 + R_3}{R_1 + R_2} V_{S_1}$

$V_{C} = \frac{R_1 + R_2 + R_3}{R_1 + R_2} V_{S_1}$

$V_{C} = \frac{R_2 + R_3}{R_1 + R_2} V_{S_1}$

$V_{C} = \frac{R_2 + R_3}{R_1 + R_2} V_{S_1}$

$V_{S_2} = V_{A_1} = V_{A_2} = \frac{R_2 + R_3}{R_1 + R_2} V_{S_2}$

((i) :  $A_{C} = V_{C} = 0 \Rightarrow V_{C} = 0$ ;  $V_{A} = V_{S_2} = 0$

$V_{C} = V_{C} = 0 \Rightarrow V_{C} = 0$ ;  $V_{C} = V_{C} = \frac{R_2 + R_2}{R_1} (R_1 | R_2) I_{C}$

$V_{C} = \frac{R_2 + R_3}{R_1 + R_2} V_{C} \Rightarrow V_{C} = \frac{R_2 + R_2}{R_1} (R_1 | R_2) I_{C}$

#### 3. (10 points)

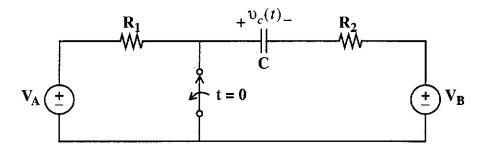

Figure 3

The circuit of Figure 3, is in equilibrium for t < 0. The switch is opened at t = 0.

a) (5 points)

Determine the capacitor voltage  $v_c(t)$  for t > 0.

$$V_c(t)$$

=  $(V_{A*}-V_B)$  +  $\mathcal{R}(-V_A)e^{-(R_1+R_2)C}$

b) (5 points)

Determine the total energy dissipated in  $R_1$  and  $R_2$  combined, during the transient after the switch is opened at t = 0.

#### 4. (15 points)

| A | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

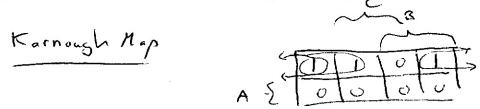

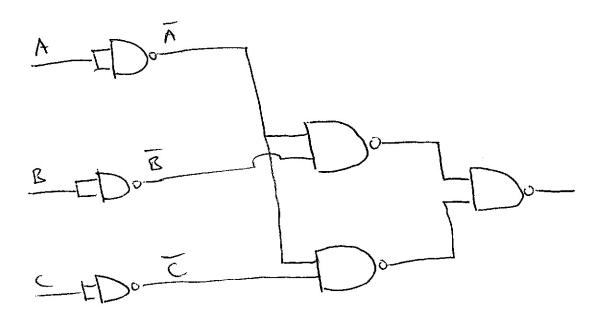

Figure 4

# a) (5points) In the truth table of Figure 4, consider A, B and C as inputs and F as output. Write F as a sum-of-products expression.

b) (5 points)

Generate a minimal sum-of-products expression for F.

## 4. (continued)

c) (5 points)

Draw a logic implementation of your minimal sum-of-products from part (b), using only NAND gates.

## 5. (10 points)

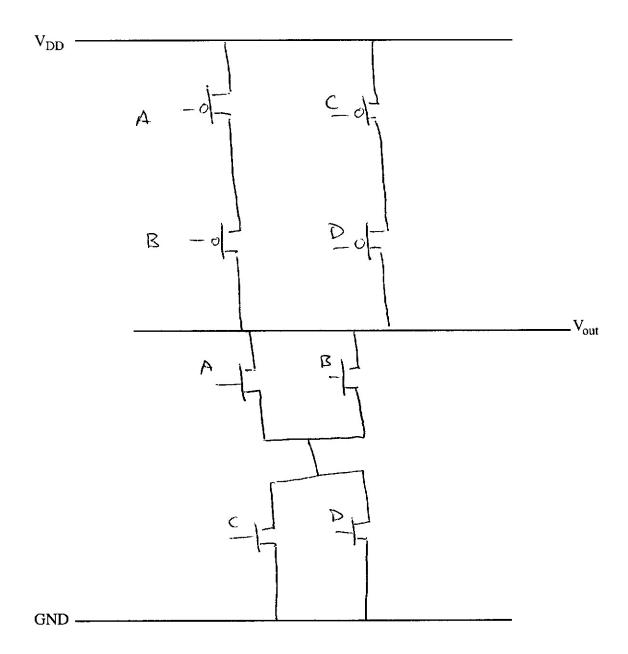

Consider the logic expression  $F = \overline{(A+B)} + \overline{(C+D)}$ .

Draw a CMOS implementation of this logic function in the diagram below. You will need to specify the pull-up network and the pull-down network.

$$\overline{F} = (A+B) \cdot (C+D)$$

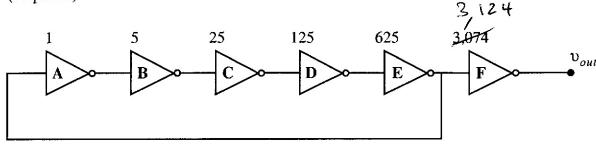

Figure 6

Figure 6 shows a ring oscillator implemented with a buffer structure. Inverter  ${\bf A}$  on the far left is a basic inverter with  $R_p=6k\Omega$ ,  $R_n=4k\Omega$  and  $C_G=5fF$ . We only consider gate capacitance in this problem. Inverter  ${\bf B}$  is exactly five times bigger (i.e.  $W_{n_B}=5W_{n_A}$ ;  $W_{p_B}=5W_{p_A}$ ) than inverter  ${\bf A}$ . Analogously, the relative sizes of inverters  ${\bf C}$ ,  ${\bf D}$ ,  ${\bf E}$  and  ${\bf F}$  are shown in Figure 6. Suppose  $V_{iL}=\frac{1}{e}V_{DD}$  and  $V_{iH}=\left(1-\frac{1}{e}\right)V_{DD}$ .

Determine the frequency of oscillation for the ring oscillator of Figure 6.

For each slage,

$$T_{V_{DD}} \rightarrow V_{iL} = 5.20 pS = 100 pS$$

$$T_{O} \rightarrow V_{iH} = 5.30 pS = 150 pS$$

$$T = 5.250 pS$$

$$= 1.25 nS$$

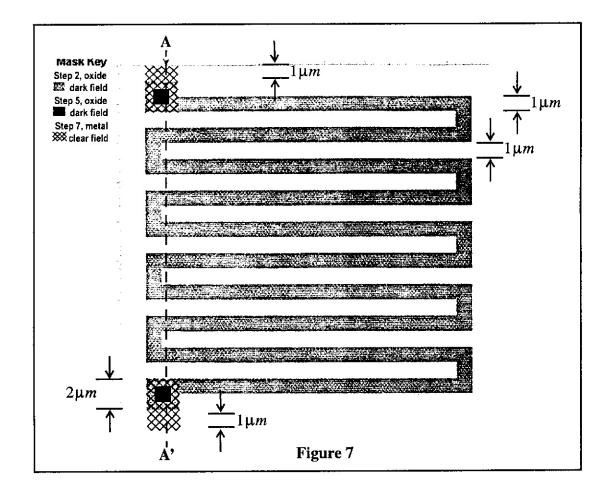

#### 7. (15 points)

A process for fabrication of a diffusion resistor is as follows:

- 0) Begin with lightly doped p-type Si substrate.

- 1) Grow SiO<sub>2</sub> to a thickness of 500 nm.

- 2) Pattern SiO<sub>2</sub> with a dark field mask that defines the resistor pattern.

- 3) Implant donors with a concentration of 10<sup>8</sup> ions/cm<sup>2</sup> and anneal uniformly to a depth of 500 nm.

- 4) Deposit SiO<sub>2</sub> to a thickness of 625 nm.

- 5) Pattern SiO<sub>2</sub> with a dark field mask that defines the contacts.

- 6) Deposit Al to a thickness of  $1\mu m$ .

- 7) Pattern Al with a clear field mask.

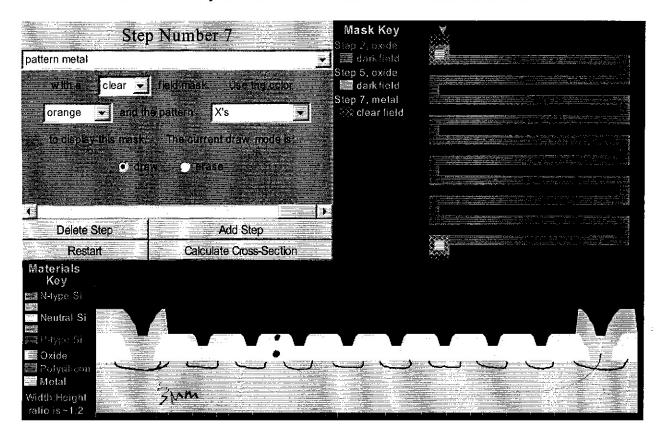

Masks for this problem are shown in Figure 7.

#### a) (10 points)

Draw a neat cross-section of the fabricated device for the cross-section A-A' shown in the figure.

### b) (5 points)

Determine the sheet resistance of the diffusion layer in this technology.

Take  $\mu_n = 300 \frac{cm^2}{v-s}$  and the charge of an electron as  $-1.6 \times 10^{-19} C$ . Make and explain approximations as necessary.

$$N_{\rm p} = \frac{10^8/{\rm cm}^2}{t}$$

$t = depth$

$$\sigma t = 300 \frac{\text{cm}^2}{\text{V-S}} \cdot (1.6 - 10^{-19} \text{c}) \cdot 10^8 / \text{cm}^2$$

$$= 4.8 \cdot 10^{-9} \Rightarrow R_s = 0.2 \cdot 10^9 = 2.10^8$$

7 (a)

## SIMPLer version 1.1

Too big? Try hiding the button and location gadgets in your browser. Too small? Try the 800x600 version or the 1000x760 version

Help file