Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

## EECS 42 Introduction to Electronics for Computer Science Andrew R. Neureuther

## Lecture # 11 Logic Implementation

- Logic Levels and Gate Circuits

- Combination of Logic Functions

- Synthesis from a Truth Table

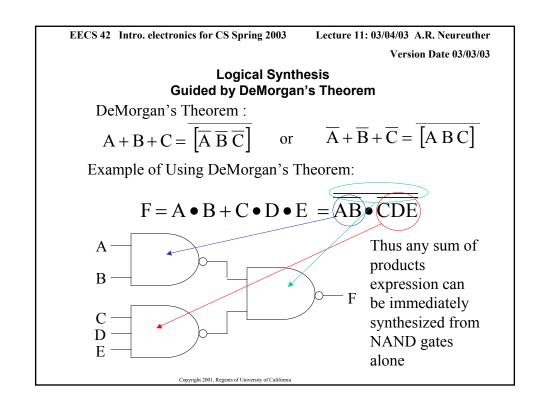

- NAND Gate Synthesis

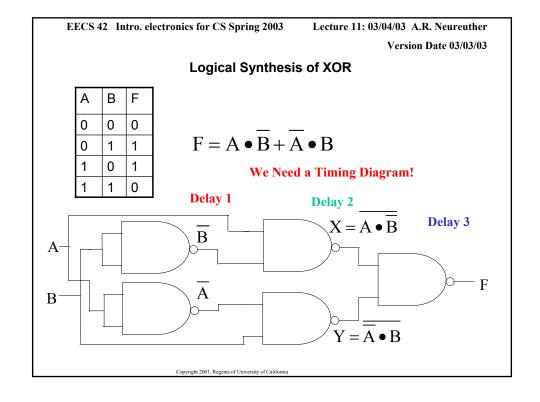

- XOR and Introduction to Timing

http://inst.EECS.Berkeley.EDU/~ee42/

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003 Lecture 11: 03

Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

### Game Plan 03/04/03

#### Monday 03/04/04

- □ Review

- ☐ Logic Implementation: 11.2-11.3 pp. 403-422

#### Wednesday 03/05/03:

■ Midterm In Class, Closed Book, Closed Notes, Paper Provided, Bring Calculator

### Next (8th) Week:

- ☐ Monday: Physical Limits of Logic

- □ Wednesday: Dependent Sources

No Problem Set Due 7th week.

Problem set #6 out Monday 3/3 and due at 2:30 3/10 in box in 240 Cory

Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

#### REMINDER

Midterm March 5th, 3:10-4:03 PM Closed Book, Closed Notes, Bring Calculator, Paper Provided

**Old Exams Are Posted on Web**

Review Session 5-7 Mon 3/4/04 in 241 Cory

**EE 43 Labs Are Not Cancelled but will be light:**

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

# First Midterm Exam: Topics

- Basic Circuit Analysis (KVL, KCL)

- Equivalent Circuits and Graphical Solutions for Nonlinear Loads

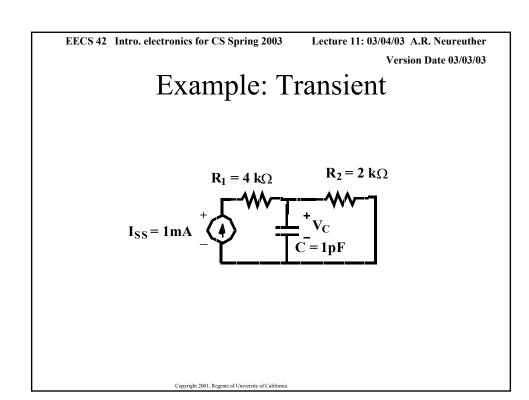

- Transients in Single Capacitor Circuits

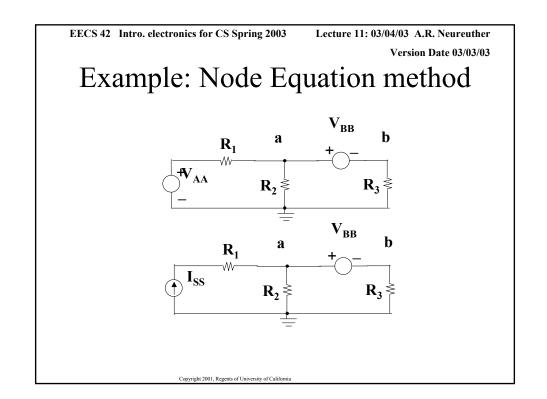

- Node Analysis Technique and Checking Solutions

Exam is in class 3:10-4:03 PM, Closed book, Closed notes, Bring a calculator, Paper provided

Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

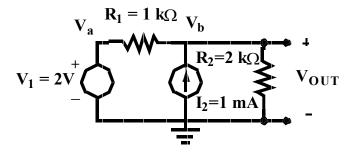

# Example: Basic Circuit Analysis

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

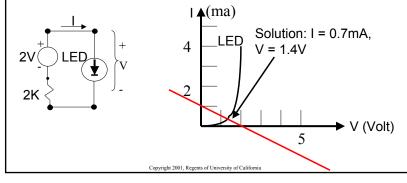

### **Example: Load-Line Method**

Lets hook our 2K resistor + 2V source circuit up to an LED (light-emitting diode), which is a very nonlinear element with the IV graph shown below.

Again we draw the I-V graph of the 2V/2K circuit on the same axes as the graph of the LED. Note that we have to get the sign of the voltage and current correct!! (The sign of the current is reversed from  $I_{SC}$ )

At the point where the two graphs intersect, the voltages and the currents are equal, in other words we have the solution.

Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

#### **Some Important Logical Functions**

• "AND"

$A \cdot B$  (or  $A \cdot B \cdot C$ )

•. "OR"

A+B (or A+B+C+D...)

"INVERT" or "NOT"

not A (or  $\overline{A}$ )

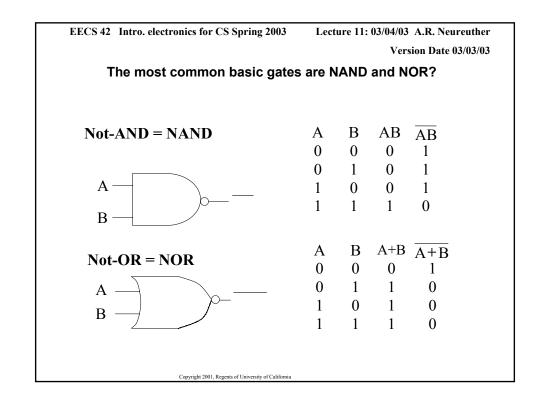

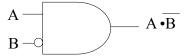

• "not AND" = NAND

$\overline{AB}$  (only 0 when A and B=1)

• "not OR" = NOR

$\overline{A+B}$  (only 1 when A=B=0)

• exclusive OR = XOR

$A \oplus B$  (only 1 when A, B differ) i.e., A + B except  $A \cdot B$

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003 Lecture 11: 03/04/03 A.R. Neureuther

Logic Gates Version Date 03/03/03

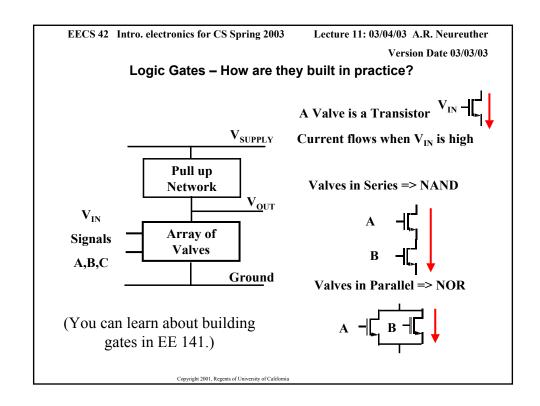

These are circuits that accomplish a given logic function such as "OR". We will shortly see how such circuits are constructed. Each of the basic logic gates has a unique symbol, and there are several additional logic gates that are regarded as important enough to have their own symbol. The set is: AND, OR, NOT, NAND, NOR, and EXCLUSIVE OR.

$$A \longrightarrow OR$$

$C=A+B$   $B \longrightarrow NOR$   $C=C=C=C$

EECS 42 Intro. electronics for CS Spring 2003 Logic Circuits

Lecture 11: 03/04/03 A.R. Neureuther S Version Date 03/03/03

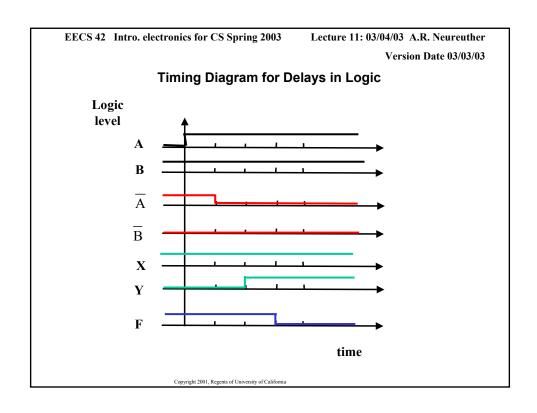

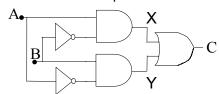

With a combination of logic gates we can construct any logic function. In these two examples we will find the truth table for the circuit.

It is helpful to list the intermediate logic values (at the input to the OR gate). Let's call them X and Y.

Now we complete the truth tables for X and Y, and from that for C. (Note that  $X = A \bullet B$  and  $Y = B \bullet A$  and finally C = X + Y)

| Α | В | Х | Y | С |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 |

Interestingly, this is the same truth table as the EXCLUSIVE OR

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 11: 03/04/03 A.R. Neureuther

Version Date 03/03/03

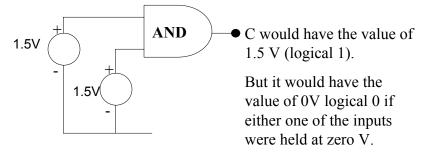

Logic Gates - How are they used in practice?

First of all we must agree on what is High (logical 1) or low (logical 0). Suppose 1.5 V is 1 and 0V is logical 0.

Lecture 11: 03/04/03 A.R. Neureuther

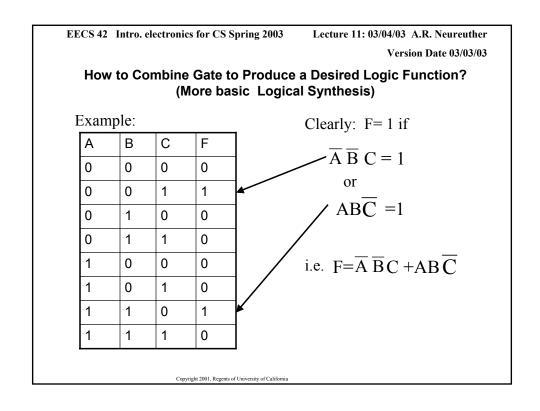

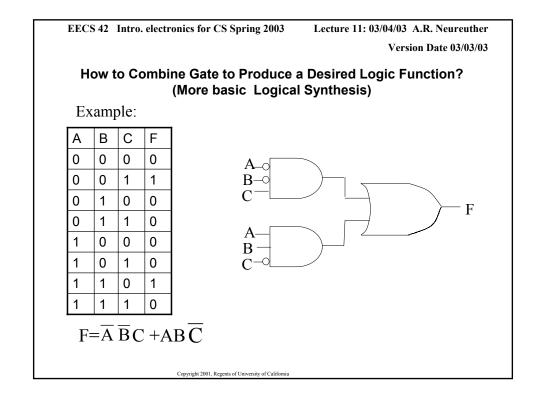

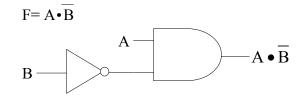

# How to Combine Gate to Produce a Desired Logic Function? 13 (More basic Logical Synthesis)

Again a little shorthand is useful

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 11: 03/04/03 A.R. Neureuther Version Date 03/03/03

# How to Combine Gate to Produce a Desired Logic Function? (More basic Logical Synthesis)

Suppose we are given a truth table (all logic statements can be represented by a truth table). How can we implement the function?

**Answer:** There are lots of ways, but one simple way is implementation from "sum of products" formulation.

**How to do this:** 1) Write sum of products expression from truth table and 2) Implement using standard gates.

(Warning this is probably inefficient – we need to minimize, or simplify the expression. You will learn this in CS 150.)