EECS 42 Intro. electronics for CS Spring 2003

Lecture 12: 03/10/03 A.R. Neureuther

Version Date 03/09/03

# EECS 42 Introduction to Electronics for Computer Science Andrew R. Neureuther

## Lecture # 12 Physical Limits of Logic

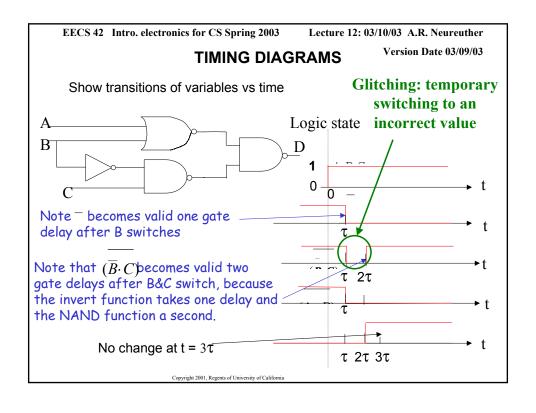

- Timing Diagrams

- capacitance Loading

http://inst.EECS.Berkeley.EDU/~ee42/

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 12: 03/10/03 A.R. Neureuther

Version Date 03/09/03

### Game Plan 03/10/03

### Monday 03/10/04

Monday: Physical Limits of Logic (11.3, 11.4 pp 403-422)

### Wednesday 03/12/03:

**□** Dependent Sources (4.1 and 4.3)

### Next (9th) Week:

- Monday: Circuit analysis with dependent sources (4.1-4.3)

- Wednesday: Comparators and op-amps (handout)

Problem set #6: out Monday 3/3 and due at 2:30 3/10 in box in 240 Cory – logic functions, truth tables, synthesis, timing diagram

Problem set #7: out Monday 3/10 and due at 2:30 3/10 in box in 240 Cory – timing diagram, ca

# EECS 42 Intro. electronics for CS Spring 2003 Lecture 12: 03/10/03 A.R. Neureuther Logic Gates Version Date 03/09/03

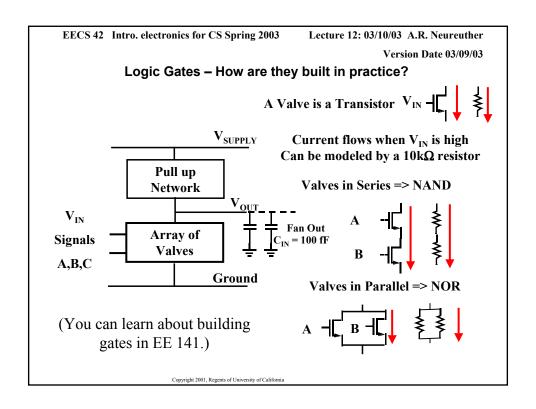

These are circuits that accomplish a given logic function such as "OR". We will shortly see how such circuits are constructed. Each of the basic logic gates has a unique symbol, and there are several additional logic gates that are regarded as important enough to have their own symbol. The set is: AND, OR, NOT, NAND, NOR, and EXCLUSIVE OR.

A AND

$$C=A \cdot B$$

$B$  NAND  $C=\overline{A} \cdot \overline{B}$

A NAND  $C=\overline{A} \cdot \overline{B}$

A NOR  $C=\overline{A} + \overline{B}$

A NOR  $C=\overline{A} + \overline{B}$

A  $C=A+B$

B  $C=A+B$

A  $C=A+B$

B  $C=A+B$

B  $C=A+B$

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003 Lecture 12: 03/10/03 A.R. Neureuther Logic Circuits Version Date 03/09/03

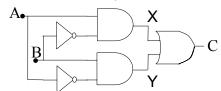

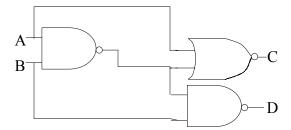

With a combination of logic gates we can construct any logic function. In these two examples we will find the truth table for the circuit.

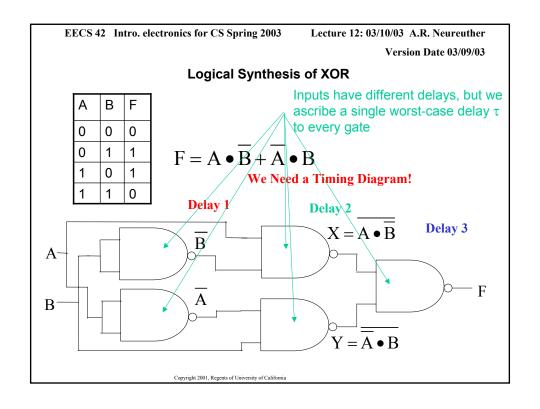

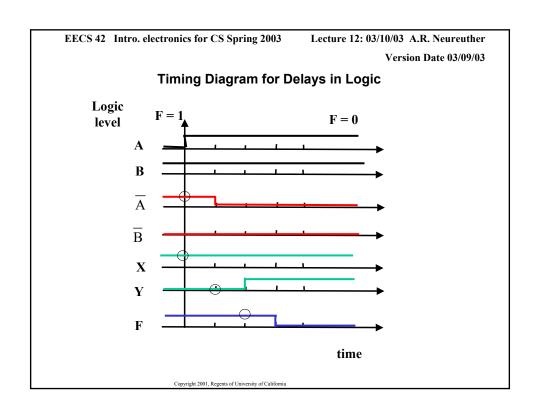

It is helpful to list the intermediate logic values (at the input to the OR gate). Let's call them X and Y.

Now we complete the truth tables for X and Y, and from that for C. (Note that  $X=A\bullet \overline{B}$  and  $Y=B\bullet \overline{A}$  and finally C=X+Y)

| Α | В | Х | Y | С |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 |

Interestingly, this is the same truth table as the EXCLUSIVE OR

Lecture 12: 03/10/03 A.R. Neureuther

Version Date 03/09/03

#### What Are Some Limitations of Digital?

It takes a lot of bits to represent even simple audio signals and if we convert a real-time audio signal to digital, we need to transmit a lot of bits every second.

**Example:** An ordinary audio signal is sampled every 50µs (to achieve 10KHz frequency performance) and evaluated (converted to digital form) to an accuracy of 1 part in 10,000. Every sample requires how many bits?

$2^{13}$  = 8,192 and  $2^{14}$  = 16,384 so we need 14 bits for each sample. Now we need to transmit these bits 20,000 times per second. The bit rate is 280,000 baud!}

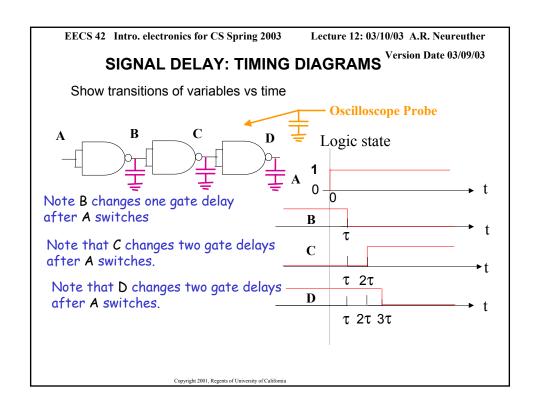

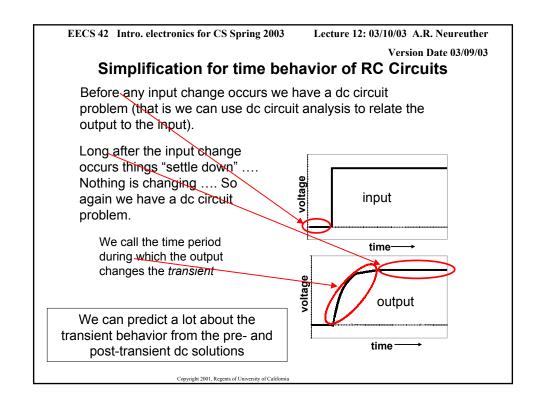

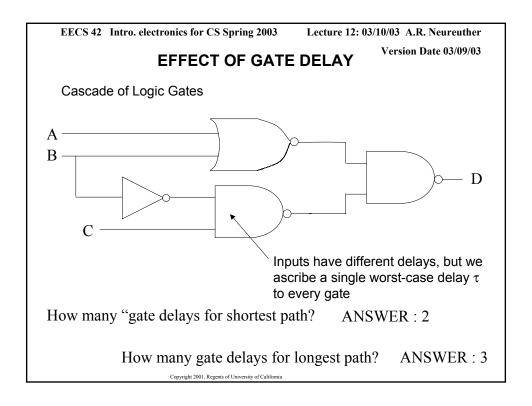

The transmission of digital signals as pulses through circuits and over transmission media leads to pulse degradation, just as analog signals are degraded. As a consequence, we must (a) detect and regenerate the signal before it gets "buried in the noise," and (b) accept that propagation delays are intrinsic to signal flow, and take these delays into account in our design (e.g., to avoid making a control decision based on a piece of information that has not yet arrived!). The RC transient lectures treated pulse degradation in real circuits quantitatively.

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 12: 03/10/03 A.R. Neureuther

Version Date 03/09/03

### PHYSICAL LIMITATIONS OF LOGIC GATES

- Computer Datapath: Boolean algebraic functions using binary variables

- Symbolic representation of functions using logic gates

NOR

$$\overline{A+B} = C \rightarrow A$$

NAND  $\overline{AB} = C \rightarrow A$

B

O

### However:

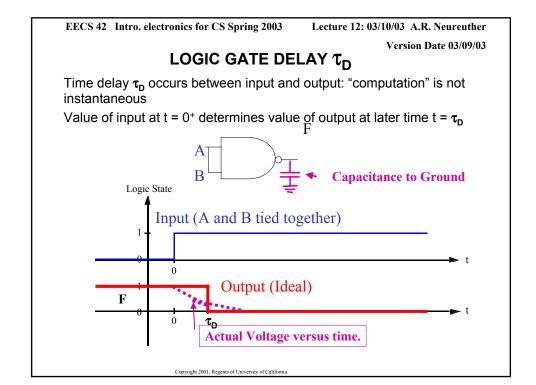

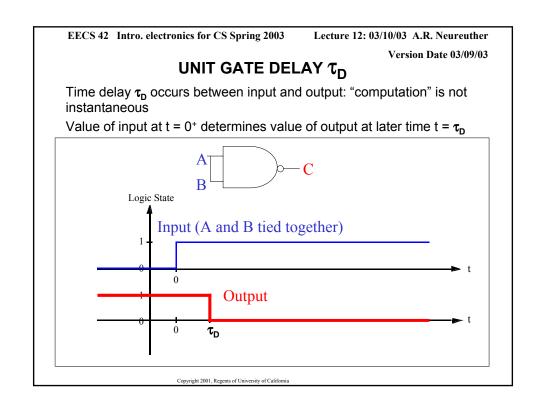

• Every node has capacitance and interconnects have resistance. It takes time to charge these capacitances.

Thus, output of all circuits, including logic gates is **delayed** from input.

EECS 42 Intro. electronics for CS Spring 2003

Lecture 12: 03/10/03 A.R. Neureuther

Version Date 03/09/03

### PHYSICAL LIMITATIONS OF LOGIC GATES

Computer Datapath: Connected logic gates

Every node in any circuit (such as the internal circuit of a NAND gate) has capacitance and all interconnects have resistance. Thus it takes time to charge these capacitances.

Thus, output of all circuits, including logic gates is **delayed** from input.