EECS 42 Intro. electronics for CS Spring 2003 Lecture 18: 04/0703 A.R. Neureuther

Version Date 04/05/03

EECS 42 Introduction to Electronics for

# EECS 42 Introduction to Electronics for Computer Science

### Andrew R. Neureuther

#### **Lecture # 18 Logic Transients**

Handout of Mon Lecture.

- A) Quiz 4/9 and Midterm 4/16 review

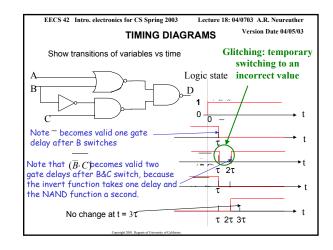

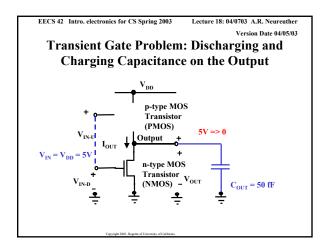

- B) Transient as Capacitor Charging

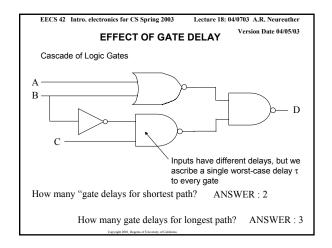

- C) Equivalent Resistance for MOS

- D) Inverter Propagation Delay

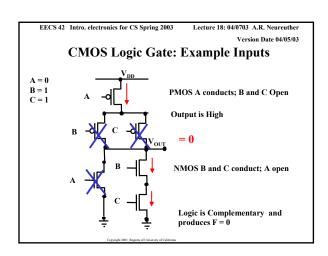

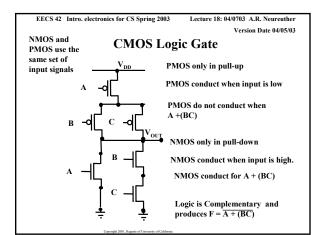

- E) Complementary MOS Operation

http://inst.EECS.Berkeley.EDU/~ee42/

Committee 2001 Resents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 18: 04/0703 A.R. Neureuther Version Date 04/05/03

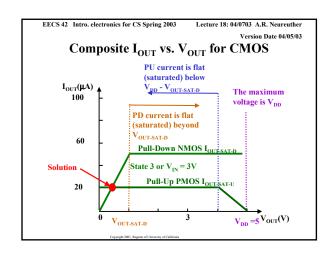

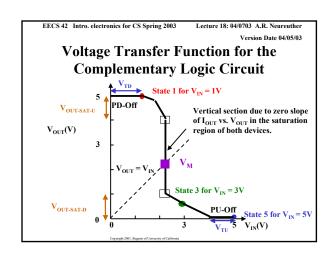

Method for Finding  $V_M$ At  $V_M$ ,

1)  $V_{OUT} = V_{IN} = V_M$ 2) Both devices are in saturation

3)  $I_{OUT-SAT-D} = I_{OUT-SAT-U}$   $I_{OUT-SAT-D} = k_D (V_N) - V_{TD}) V_{OUT-SAT-D}$   $= I_{OUT-SAT-U} = k_U (V_{DR}) - V_{TU} V_{OUT-SAT-U}$ Substitute  $V_M$ Solve for  $V_M$ Example Result: When  $k_D = k_P$ ,  $V_{OUT-SAT-D} = V_{OUT-SAT-U}$  and  $V_{TD} = V_{TU}$ , then  $V_M = V_{DD}/2$

Corputable Manager of Control of the propagation of the first of the original form of the propagation of the first of the original form of the propagation of the first of the original form of the propagation of the propa

EECS 42 Intro. electronics for CS Spring 2003

Lecture 18: 04/0703 A.R. Neureuther

Version Date 04/05/03

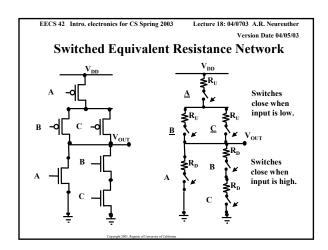

### **Switched Equivalent Resistance Model**

The above model assumes the device is an ideal constant current source.

- 1) This is not true below  $\boldsymbol{V}_{\text{OUT-SAT-D}}$  and leads to in accuracies.

- 2) Combining ideal current sources in networks with series and parallel connections is problematic.

Instead define an equivalent resistance for the device by setting 0.69  $R_{D}\mathrm{C}$  equal to the  $\Delta t$  found above

\_\_\_\_

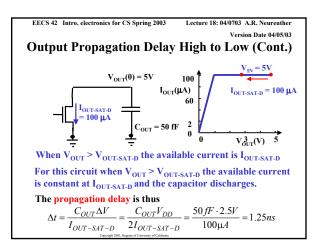

$\Delta t = \frac{C_{OUT}V_{DD}}{2I_{OUT-SAT-D}} = 0.69R_DC_{OUT}$

$$R_D = \frac{V_{DD}}{2 \cdot (0.69) I_{OUT-SAT-D}} \approx \frac{3}{4} \frac{V_{DD}}{I_{OUT-SAT-D}} = \frac{3}{4} \frac{5V}{100\mu A} = 37.5k\Omega$$

Each device can now be replaced by this equivalent resistor.

Copyright 2001, Regents of I

EECS 42 Intro. electronics for CS Spring 2003

cture 18: 04/0703 A.R. Neureuther Version Date 04/05/03

Version Date 04/05

## $\frac{3}{4}$ $V_{DD}/I_{SAT}$ Physical Interpretation

$^{3}\!\!/_{4}\,V_{DD}$  is the average value of  $\,V_{OUT}$

Approximate the NMOS device curve by a straight line from (0,0) to ( $I_{OUT\text{-}SAT\text{-}D},\,^{3}\!\!/\,\,V_{DD}$  ).

Interpret the straight line as a resistor with

slope =

$$1/R = \frac{3}{4} V_{DD}/I_{SAT}$$

Conversely 2001. Research of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 18: 04/0703 A.R. Neureuther

Version Date 04/05/03

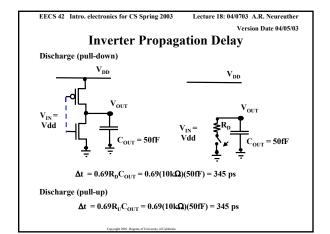

#### **Switched Equivalent Resistance Values**

The resistor values depend on the properties of silicon, geometrical layout, design style and technology node.

n-type silicon has a carrier mobility that is 2 to 3 times higher than p-type.

The resistance is inversely proportion to the gate width/length in the geometrical layout.

Design styles may restrict all NMOS and PMOS to be of a predetermined fixed size.

The current per unit width of the gate increases nearly inversely with the linewidth.

For convenience in EE 42 we assume  $R_D$  =  $R_U$  = 10 k $\Omega$

Copyright 2001, Regents of University of California