EECS 42 Intro. electronics for CS Spring 2003

Lecture 20: 04/14/03 A.R. Neureuther

Version Date 04/05/03

## EECS 42 Introduction to Electronics for Computer Science Andrew R. Neureuther

### **Lecture # 20 Logic Transients**

Handout of Monday Lecture.

- A) 2<sup>nd</sup> Midterm Review (Cont.)

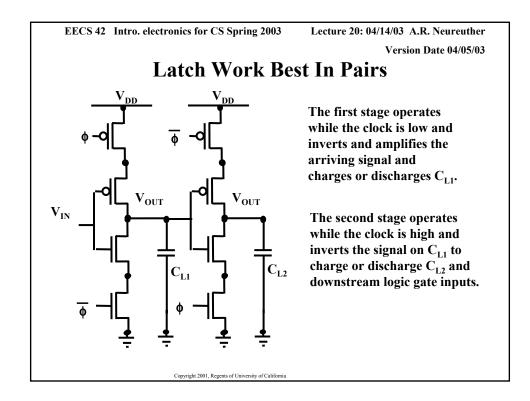

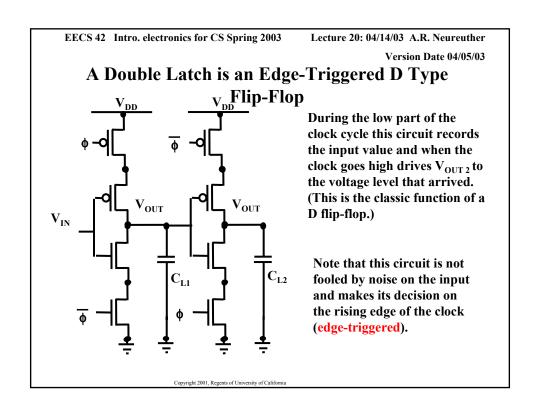

- B) Latch circuit to hold/release signals

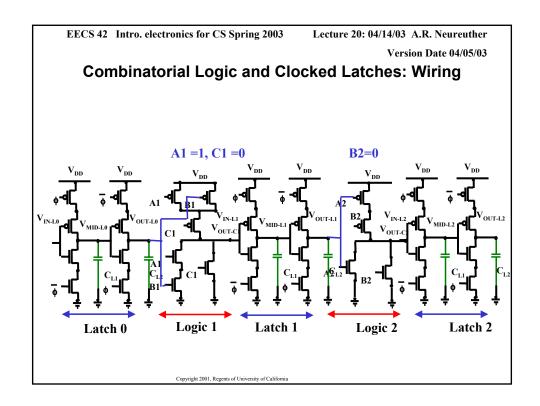

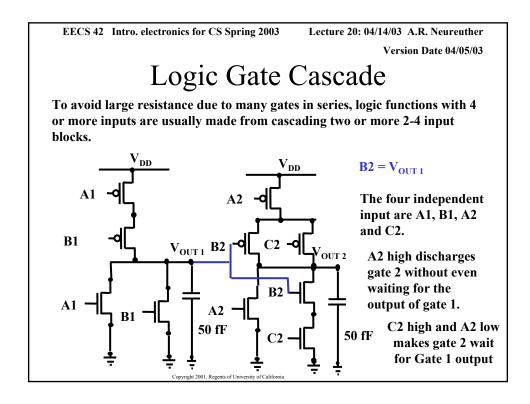

- C) Cascade CMOS elements with latches

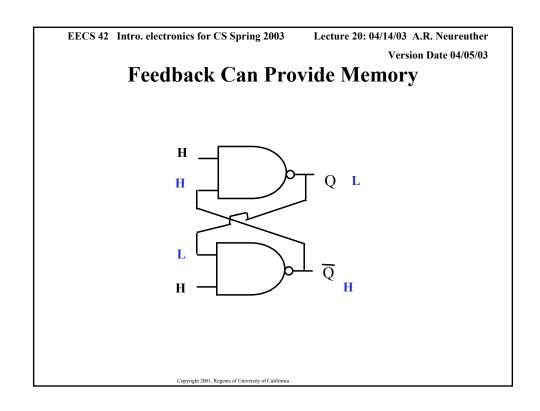

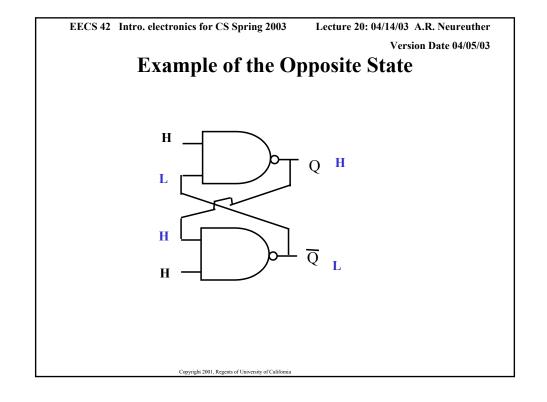

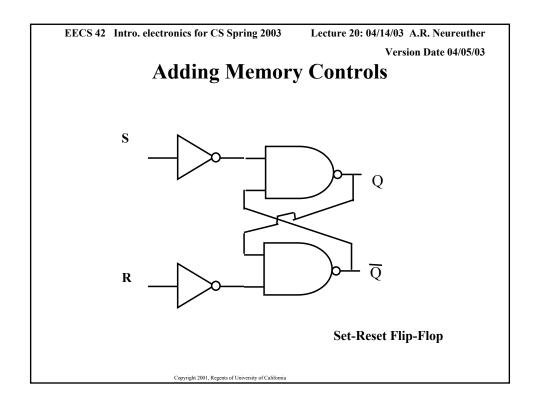

- D)Logic Feedback creates memory http://inst.EECS.Berkeley.EDU/~ee42/

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003

Lecture 20: 04/14/03 A.R. Neureuther

Version Date 04/05/03

## Game Plan 04/14/03

Last Week: Logic Delay; resistor model, CMOS operation and delay

#### Monday 4/14/03:

- □ 2<sup>nd</sup> Midterm review (Cont.)

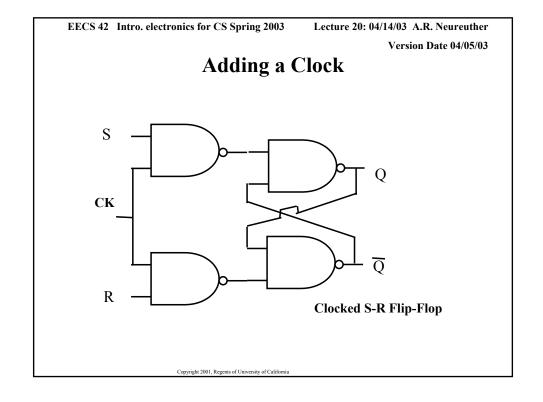

- ☐ CMOS Latch and use in logic cascade

- ☐ Feedback in logic to produce memory

#### Wednesday 04/09/03:

☐ 2<sup>nd</sup> Midterm

Next (13th) Week: Diodes and MOS Operation

No Problem set for 4/16 as Midterm 4/16: Lectures 1-17 with emphasis on Lectures 10-17; Review Session Monday 5:30-7PM

Problem set #10 for 4/23: Logic Delay

Copyright 2001, Regents of University of California

Lecture 20: 04/14/03 A.R. Neureuther

Version Date 04/05/03

# Data Synchronization problem

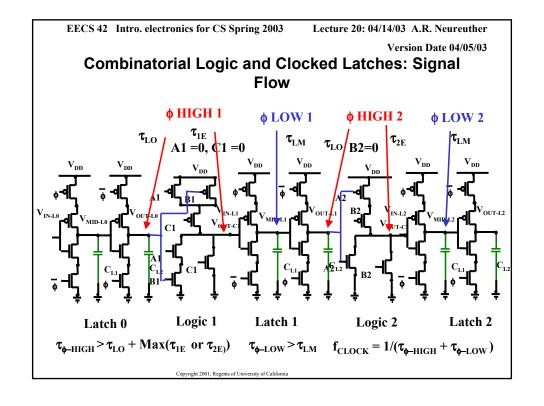

- Combinatorial logic gates can give incorrect answers prematurely and may take several gate propagation delays produce an answer.

- Clocks (signals as to when to proceed) and latches (which capture and hold the correct outputs) can provide synchronization.

Copyright 2001, Regents of University of California

EECS 42 Intro. electronics for CS Spring 2003 Lecture 20: 04/14/03 A.R. Neureuther

Version Date 04/05/03

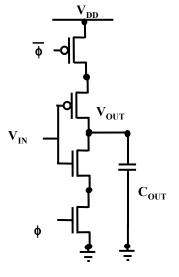

## Latch Controlled by a Clock

An inverter with clocked devices in series can form a latch.

When the clock  $\phi$  is high its complement  $\overline{\phi}$  is low and the inverter operates.

To synchronize the data the clock remains low until the data is correct at all locations on the chip. When the clock goes high the inverse of the data is passed.

Copyright 2001, Regents of University of California