## EECS151/251A Midterm 1

Review Session

Zhenghan Lin & Harrison Liew

## Midterm Logistics

- Finish your practice exam ASAP!

- Remember, everything must emulate the exam day environment/sequence

- Exam: Oct. 6 @ 3:40pm 5:00pm PST (except for approved accommodations)

- PDF format, 5 questions + subparts

- Mostly handwritten (drawing diagrams, multiple choice selections, not the same as previous midterm formats)

- No long-form written answers, only some short answers

- You will receive an email with a Google Doc link before the exam

- Links to exam PDF, submission forms, errata

## Midterm Scope

5 questions on topics through Lecture 10

- 1. Boolean logic (translation, simplification)

- 2. FSMs (construct from specification, waveforms)

- 3. RISC-V instructions (instr. formats, address ranges, pseudo-insts)

- RISC-V datapath (Verilog of datapath/control logic, extending RV32I w/ new inst., timing)

- 5. Verilog (deduce function from code, write some small code snippets)

## Logic (FA18, Problem 1)

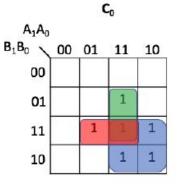

#### [PROBLEM 1] Combinational Logic Design and Optimization (10 Pts)

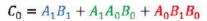

a) Consider the following truth table. Use K-maps to derive a minimized sum-of-products expression for the outputs C<sub>0</sub> and S<sub>0</sub> only. (4 Pts)

| A <sub>1</sub> | An | B, | Bo | $C_0$ | S | So |

|----------------|----|----|----|-------|---|----|

| 0              | 0  | 0  | 0  | 0     | 0 | 0  |

| 0              | 0  | 0  | 1  | 0     | 0 | 1  |

| 0              | 0  | 1  | 0  | 0     | 1 | 0  |

| 0              | 0  | 1  | 1  | 0     | 1 | 1  |

| 0              | 1  | 0  | 0  | 0     | 0 | 1  |

| 0              | 1  | 0  | 1  | 0     | 1 | 0  |

| 0              | 1  | 1  | 0  | 0     | 1 | 1  |

| 0              | 1  | 1  | 1  | 1     | 0 | 0  |

| 1              | 0  | 0  | 0  | 0     | 1 | 0  |

| 1              | 0  | 0  | 1  | 0     | 1 | 1  |

| 1              | 0  | 1  | 0  | 1     | 0 | 0  |

| 1              | 0  | 1  | 1  | 1     | 0 | 1  |

| 1              | 1  | 0  | 0  | 0     | 1 | 1  |

| 1              | 1  | 0  | 1  | 1     | 0 | 0  |

| 1              | 1  | 1  | 0  | 1     | 0 | 1  |

| 1              | 1  | 1  | 1  | 1     | 1 | 0  |

b) What function does this truth table represent? Explain in words – no gate-level drawings are required. (1 Pts)

# Logic (FA18, Problem 1)

#### [PROBLEM 1] Combinational Logic Design and Optimization (10 Pts)

a) Consider the following truth table. Use K-maps to derive a minimized sum-of-products expression for the outputs Co and So only. (4 Pts)

| Α, | A <sub>D</sub> | <b>B</b> <sub>1</sub> | Bo | $C_0$ | Sı | So |

|----|----------------|-----------------------|----|-------|----|----|

| 0  | 0              | 0                     | 0  | 0     | 0  | 0  |

| 0  | 0              | 0                     | 1  | 0     | 0  | 1  |

| 0  | 0              | 1                     | 0  | 0     | 1  | 0  |

| 0  | 0              | 1                     | 1  | 0     | 1  | 1  |

| 0  | 1              | 0                     | 0  | 0     | 0  | 1  |

| 0  | 1              | 0                     | 1  | 0     | 1  | 0  |

| 0  | 1              | 1                     | 0  | 0     | 1  | 1  |

| 0  | 1              | 1                     | 1  | 1     | 0  | 0  |

| 1  | 0              | 0                     | 0  | 0     | 1  | 0  |

| 1  | 0              | 0                     | 1  | 0     | 1  | 1  |

| 1  | 0              | 1                     | 0  | 1     | 0  | 0  |

| 1  | 0              | 1                     | 1  | 1     | 0  | 1  |

| 1  | 1              | 0                     | 0  | 0     | 1  | 1  |

| 1  | 1              | 0                     | 1  | 1     | 0  | 0  |

| 1  | 1              | 1                     | 0  | 1     | 0  | 1  |

| 1  | 1              | 1                     | 1  | 1     | 1  | 0  |

| Co                              | 80                    |

|---------------------------------|-----------------------|

| Λ Δ.                            | Bo 101 11 10          |

| 13001 11 10 M                   | 00 00                 |

| 184 0 0 0                       | 5]0 (1)               |

| 0 17 6 6 0                      | 1 0 0 1               |

|                                 | 1001                  |

|                                 | 16/11/0/16            |

| 0 01 01                         | J. J. S.              |

|                                 | 5 0                   |

| 00 ( ) ( A )                    | 3,136                 |

| <u>C</u>                        | As to                 |

| Co = A,B, + A, A, BO & A, B, Bi | 1 1 A BR              |

|                                 | S= ADBO + ADBO = ADBO |

| el drawings are required.       | 7                     |

b) What function does this truth table represent? Explain in words – no gate-level drawings are required.

(1 Pts)

## Logic (FA18, Problem 1)

#### [PROBLEM 1] Combinational Logic Design and Optimization (10 Pts)

a) Consider the following truth table. Use K-maps to derive a minimized sum-of-products expression for the outputs C<sub>0</sub> and S<sub>0</sub> only. (4 Pts)

| A <sub>1</sub> | An | <b>B</b> <sub>1</sub> | Bo | $c_0$ | S | So |

|----------------|----|-----------------------|----|-------|---|----|

| 0              | 0  | 0                     | 0  | 0     | 0 | 0  |

| 0              | 0  | 0                     | 1  | 0     | 0 | 1  |

| 0              | 0  | 1                     | 0  | 0     | 1 | 0  |

| 0              | 0  | 1                     | 1  | 0     | 1 | 1  |

| 0              | 1  | 0                     | 0  | 0     | 0 | 1  |

| 0              | 1  | 0                     | 1  | 0     | 1 | 0  |

| 0              | 1  | 1                     | 0  | 0     | 1 | 1  |

| 0              | 1  | 1                     | 1  | 1     | 0 | 0  |

| 1              | 0  | 0                     | 0  | 0     | 1 | 0  |

| 1              | 0  | 0                     | 1  | 0     | 1 | 1  |

| 1              | 0  | 1                     | 0  | 1     | 0 | 0  |

| 1              | 0  | 1                     | 1  | 1     | 0 | 1  |

| 1              | 1  | 0                     | 0  | 0     | 1 | 1  |

| 1              | 1  | 0                     | 1  | 1     | 0 | 0  |

| 1              | 1  | 1                     | 0  | 1     | 0 | 1  |

| 1              | 1  | 1                     | 1  | 1     | 1 | 0  |

b) What function does this truth table represent? Explain in words – no gate-level drawings are required. (1 Pts)

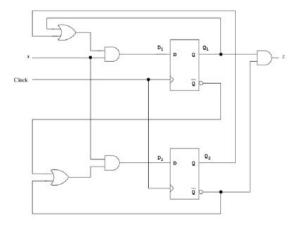

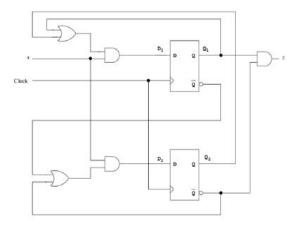

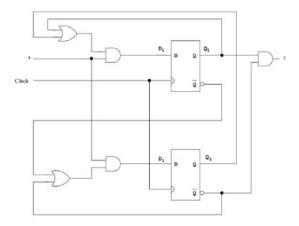

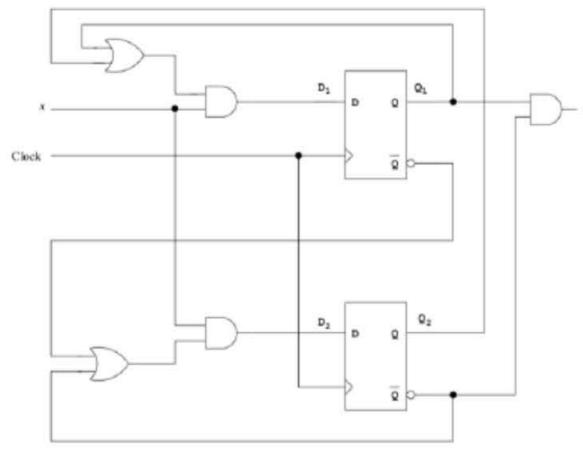

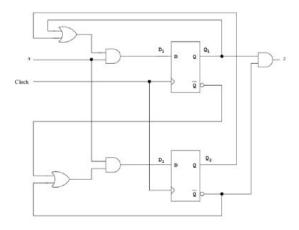

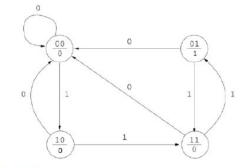

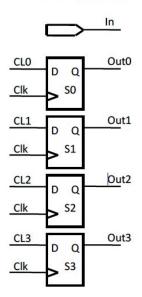

## FSM (FA18, Problem 2)

#### [PROBLEM 2] Finite State Machines (10 Pts)

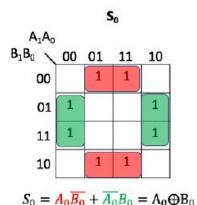

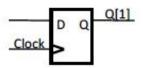

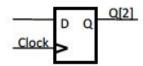

Consider the following circuit with *x* the input and *z* the output.

- a) Is this a Mealy or a Moore machine? Why? (2 Pts)

- b) Write the Boolean expressions for Flip-Flop inputs D<sub>1</sub> and D<sub>2</sub>, and the system output z. (2 Pts)

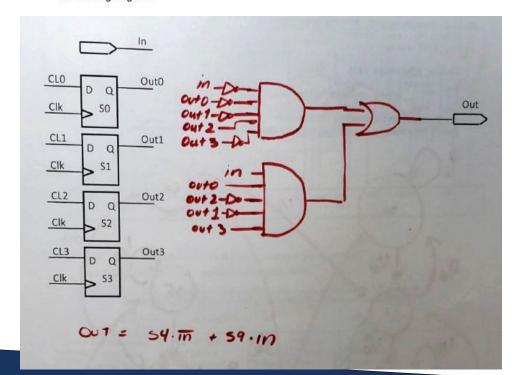

## FSM (FA18, Problem 2) Select Text Sold Text So

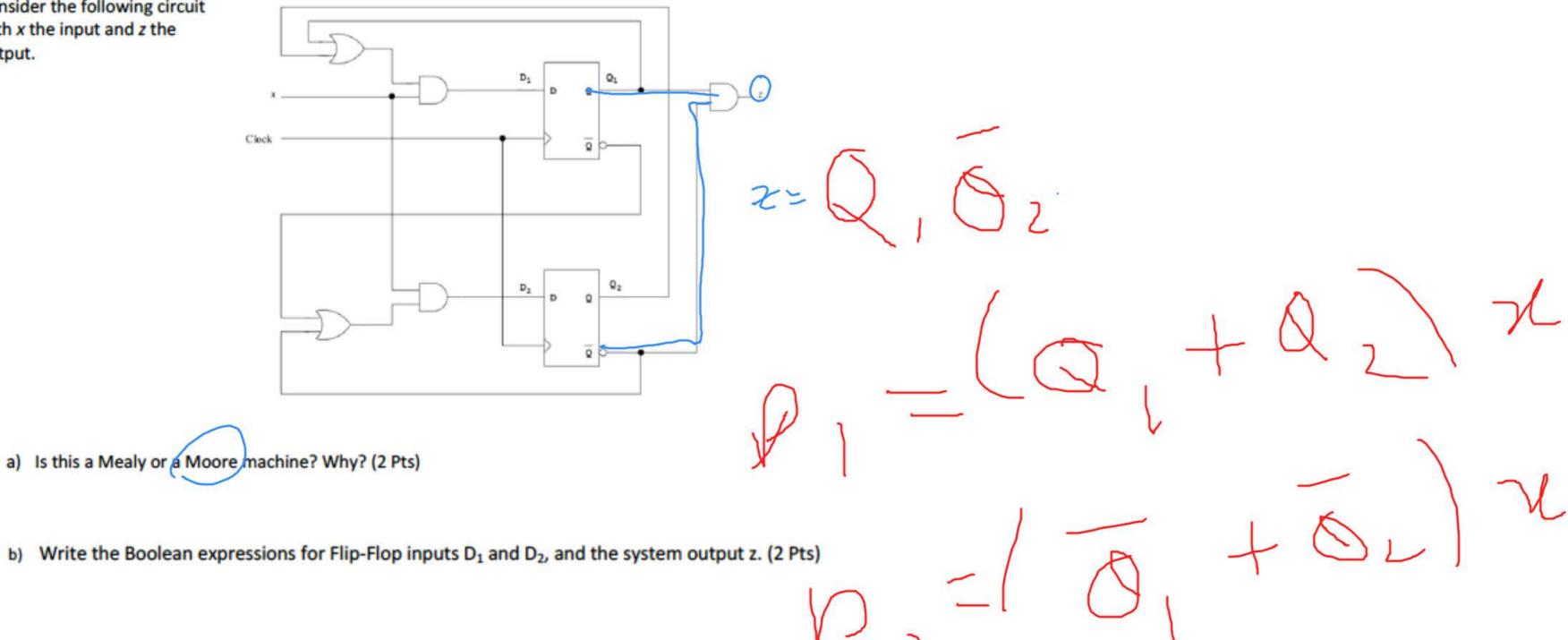

#### [PROBLEM 2] Finite State Machines (10 Pts)

Consider the following circuit with x the input and z the output.

## FSM (FA18, Problem 2)

#### [PROBLEM 2] Finite State Machines (10 Pts)

Consider the following circuit with x the input and z the output.

a) Is this a Mealy or a Moore machine? Why? (2 Pts)

This is a Moore machine. The output z depends only on the state registers  $Q_1$  and  $Q_2$ , and not on the input x.

b) Write the Boolean expressions for Flip-Flop inputs D<sub>1</sub> and D<sub>2</sub>, and the system output z. (2 Pts)

$$D_1 = x \cdot (Q_1 + Q_2)$$

$$D_2 = x \cdot (Q_1' + Q_2')$$

$$z = Q_1 Q_2$$

## FSM (FA18, Problem 2 continued)

#### [PROBLEM 2] Finite State Machines (10 Pts)

Consider the following circuit with x the input and z the output.

- c) Derive the state transition table for the circuit. (3 Pts)

- d) Draw a state diagram for the system. (3 Pts)

# FSM (FA18, Problem 2 Continued)

#### [PROBLEM 2] Finite State Machines (10 Pts)

Consider the following circuit with x the input and z the output.

c) Derive the state transition table for the circuit. (3 Pts)

d) Draw a state diagram for the system. (3 Pts)

$$b_1 = X(Q_1 + Q_2)$$

$$0_2 = X(Q_1 + Q_2)$$

$$2 = Q_1Q_2$$

| Present | Znant | Nixt | Output      |

|---------|-------|------|-------------|

| G D     | 0     | 000  | 2<br>0<br>0 |

| 0 1     | 6     | 00   | 5           |

| ( )     | 0     | 0 0  | 0           |

| يک ا    |       | 0    | 01          |

| 0       | V O   |      | 1           |

|         | 0     |      |             |

## FSM (FA18, Problem 2)

#### [PROBLEM 2] Finite State Machines (10 Pts)

Consider the following circuit with *x* the input and *z* the output.

- c) Derive the state transition table for the circuit. (3 Pts)

- d) Draw a state diagram for the system. (3 Pts)

|       | sent<br>ate | 100              |       | ext<br>ate | Output |

|-------|-------------|------------------|-------|------------|--------|

| $Q_2$ | $Q_1$       | $\boldsymbol{x}$ | $Q_2$ | $Q_1$      | Z      |

| 0     | 0           | 0                | 0     | 0          | 0      |

| 0     | 0           | 1                | 1     | 0          | 0      |

| 0     | 1           | 0                | 0     | 0          | 1      |

| 0     | 1           | 1                | 1     | 1          | 1      |

| 1     | 0           | 0                | 0     | 0          | 0      |

| 1     | 0           | 1                | 1     | 1          | 0      |

| 1     | 1           | 0                | 0     | 0          | 0      |

| 1     | 1           | 1                | 0     | 1          | 0      |

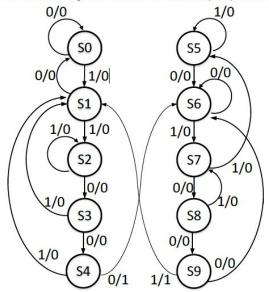

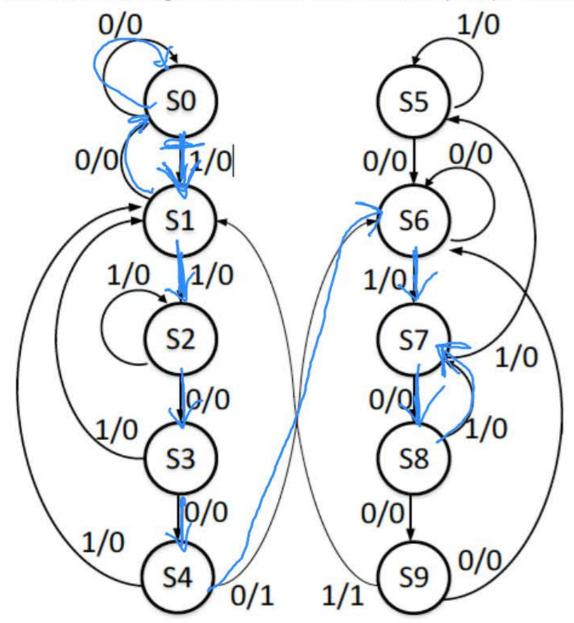

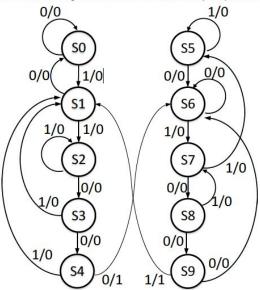

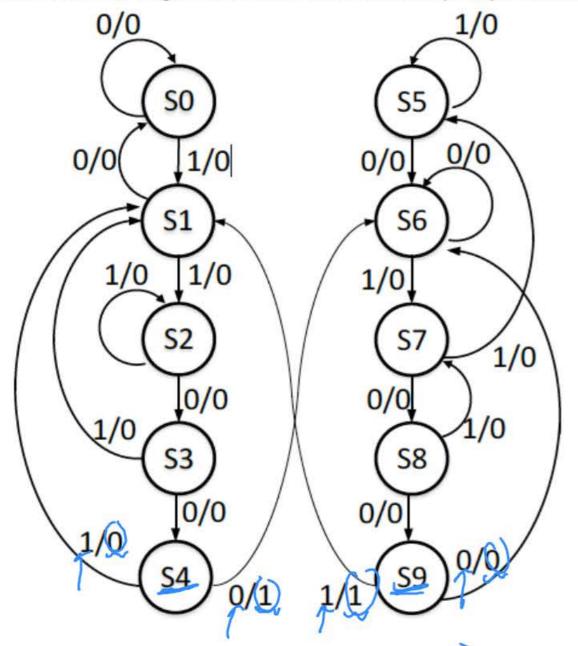

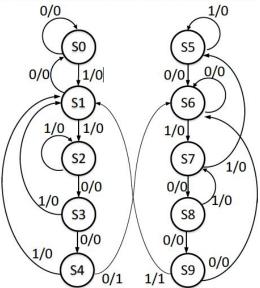

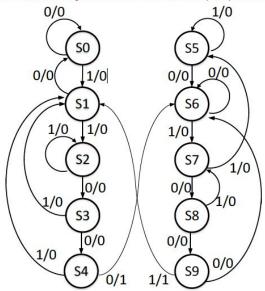

### FSM (FA19, Problem 2)

#### 2) State Machines (16 points, 20 minutes)

A state transition diagram for a finite state machine (FSM) is shown in Figure 2.

Figure 2.

- a) If the FSM starts in state S0, in which state will it be after the input pattern 01011000101?

- O S7

- O S0

- O S1

- O S2

O S8

O S5

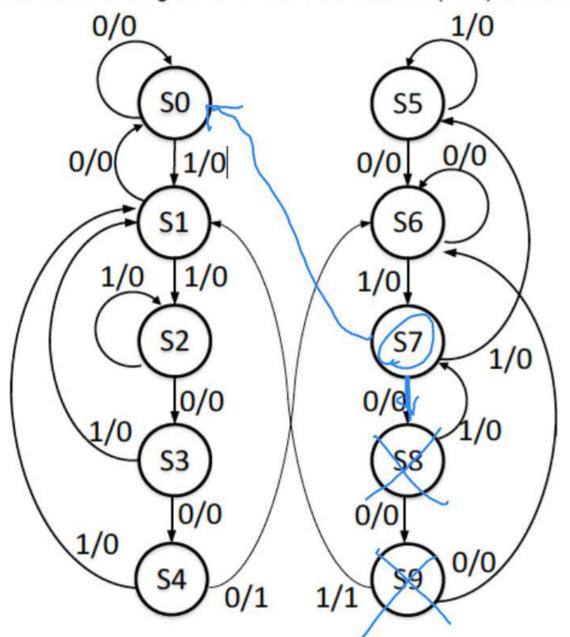

## FSM (FA19, Problem 2) Select Text Diaw Stamp Spottight

#### 2) State Machines (16 points, 20 minutes)

A state transition diagram for a finite state machine (FSM) is shown in Figure 2.

Figure 2.

a) If the FSM starts in state S0, in which state will it be after the input pattern 01011000101?

- S7

- C

- O S0

O S1

S2S9

O S8

O S6

O S4

O S3

O S5

## FSM (FA19, Problem 2 continued)

#### 2) State Machines (16 points, 20 minutes)

A state transition diagram for a finite state machine (FSM) is shown in Figure 2.

Figure 2.

#### 2) State Machines (continued)

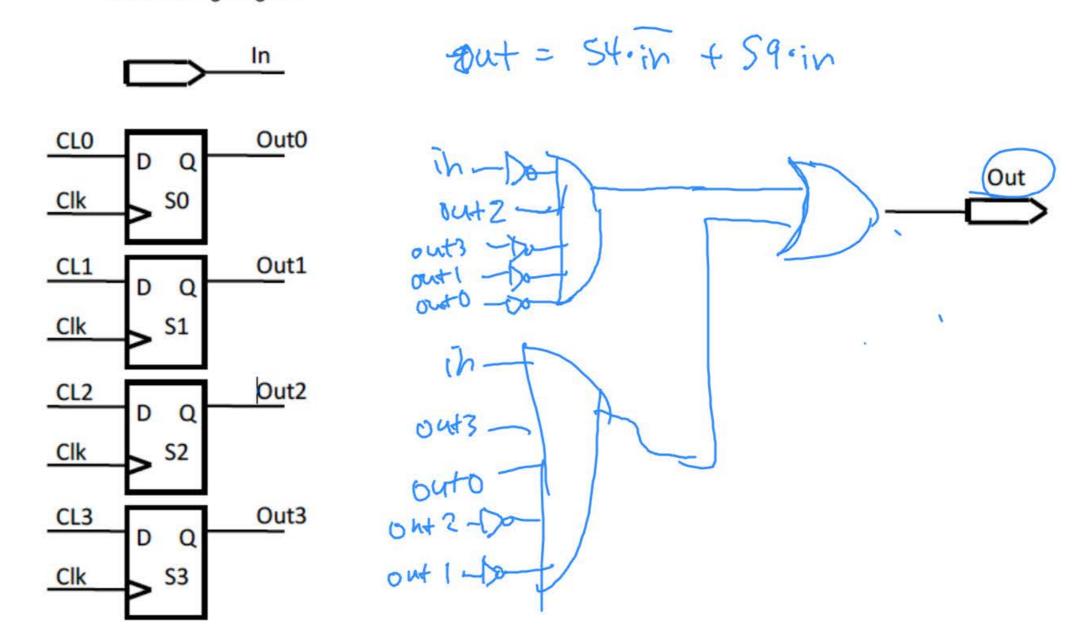

b) If the state is represented by a four-bit register S[3:0] and S4 = 4'b0100 and S9 = 4'b1001, complete the following diagram:

# FSM (FA19, Problem 2 Londing Spellight Frank Undo

#### 2) State Machines (16 points, 20 minutes)

A state transition diagram for a finite state machine (FSM) is shown in Figure 2.

Figure 2./

#### 2) State Machines (continued)

b) If the state is represented by a four-bit register S[3:0] and S4 = 4'b0100 and S9 = 4'b1001, complete the following diagram:

### FSM (FA19, Problem 2 continued)

#### 2) State Machines (16 points, 20 minutes)

A state transition diagram for a finite state machine (FSM) is shown in Figure 2.

Figure 2.

#### 2) State Machines (continued)

b) If the state is represented by a four-bit register S[3:0] and S4 = 4'b0100 and S9 = 4'b1001, complete the following diagram:

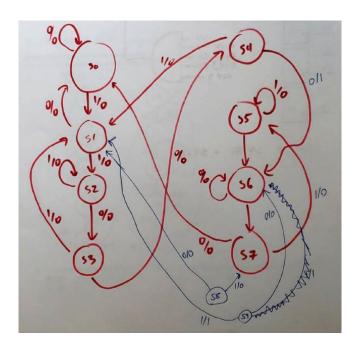

### FSM (FA19, Problem 2 continued)

#### 2) State Machines (16 points, 20 minutes)

A state transition diagram for a finite state machine (FSM) is shown in Figure 2.

Figure 2.

#### 2) State Machines (continued)

c) Your colleague wrote the following code to represent this FSM: wire[2:0] next state;

```

reg[3:0] state;

always @(posedge clk)

begin

state <= next_state;

end</pre>

```

And they also got the rest of the code correctly.

Draw a state machine diagram that corresponds to this code.

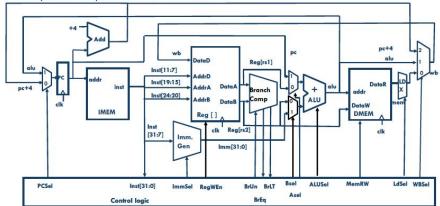

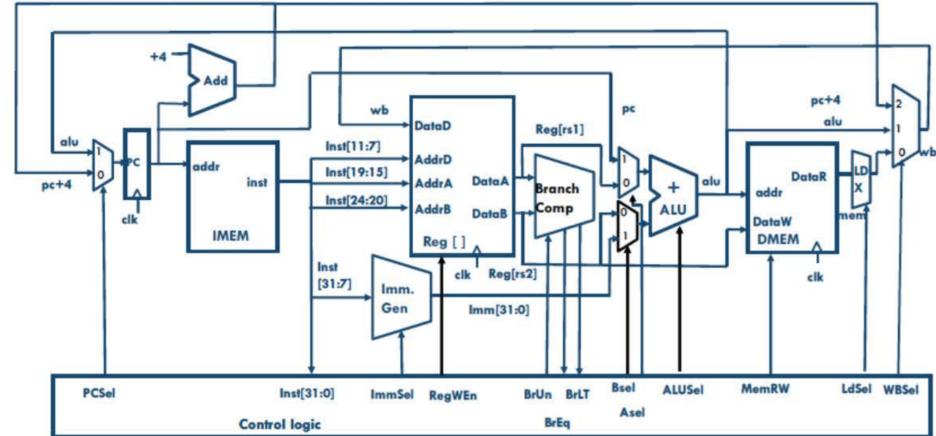

## datapathology (24 points, 25 minutes) datapath below implements the RV32l instruction set.

## FSM (FA19, Problem 2 Continued)

#### 2) State Machines (16 points, 20 minutes)

A state transition diagram for a finite state machine (FSM) is shown in Figure 2.

Figure 2.

### 2) State Machines (continued)

c) Your colleague wrote the following code to represent this FSM:

```

wire[2:0] next_state;

reg[3:0] state;

always @(posedge clk)

begin

state <= next_state;

end</pre>

```

And they also got the rest of the code correctly.

Draw a state machine diagram that corresponds to this code.

### FSM (FA19, Problem 2 continued)

#### 2) State Machines (continued)

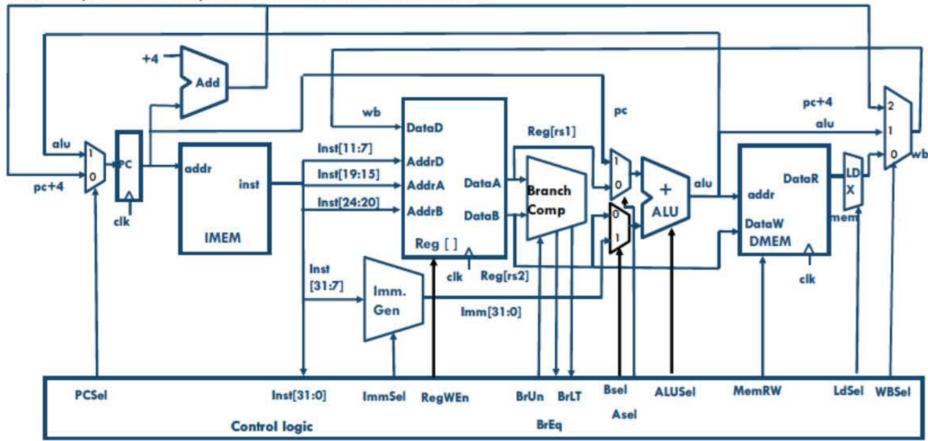

## RISC-V Datapath (FA19, Problem 3)

#### 3) Datapathology (24 points, 25 minutes)

The datapath below implements the RV32I instruction set.

a) In the RISC-V datapath above, mark what is used by a jal instruction.

jal (Jump and link): R[rd] = pc+4; pc = pc + {imm,1b'0}

| 31  | 30     | 21        | 20      | 19 12      | 11 7 | 6 0    |

|-----|--------|-----------|---------|------------|------|--------|

| imm | [20] i | .mm[10:1] | imm[11] | imm[19:12] | rd   | opcode |

|     | 1      | 10        | 1       | 8          | 5    | 7      |

|     |        | offset[2  | 0:1]    |            | dest | JAL    |

| Select<br>one per<br>row    | ASel Mux:<br>BSel Mux:     | <ul><li> "pc + 4" branch</li><li> "pc" branch</li><li> "imm" branch</li><li> "pc + 4" branch</li></ul> | <ul><li>"alu" branch</li><li>Reg[rs1] branch</li><li>Reg[rs2] branch</li><li>"alu" branch</li></ul> | <pre> * (don't care)           * (don't care)</pre> | O * (don't |

|-----------------------------|----------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|

| Select all<br>that<br>apply | Datapath units<br>RegFile: | Branch Comp Read Reg[rs1]                                                                              | ☐ Imm. Gen☐ Read Reg[rs2                                                                            | ☐ Load Extend ☐ Write Reg[rd]                       |            |

💘 EECS151/2... 🂘 Jalopnik | ... 🦞 Midterm 1 ... 🎅 Spotify Pre... 🙌 Slack | Zhe... 🚺 Signal

## 3) Datapathology (24 points, 25 minutes)

The datapath below implements the RV32I instruction set.

a) In the RISC-V datapath above, mark what is used by a jal instruction.

jal (Jump and link): R[rd] = pc+4; pc = pc + {imm, 1b'0}

| Select<br>one per<br>row    | ASel Mux:<br>BSel Mux: | O "pc + 4" branch O "pc" branch O "imm" branch O "pc + 4" branch | "alu" branch O Reg[rs1] branch O Reg[rs2] branch O "alu" branch | Commence of the Commence of th | O * (don't |

|-----------------------------|------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Select all<br>that<br>apply | Datapath units         | :   Branch Comp  Read Reg[rs1]                                   | ☐ Imm. Gen☐ Read Reg[rs:                                        | Load Extend     Write Reg[rd]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

## RISC-V Datapath (FA19, Problem 3 continued)

#### 3) Datapathology (24 points, 25 minutes)

The datapath below implements the RV32I instruction set.

a) In the RISC-V datapath above, mark what is used by a  ${\tt jal}$  instruction.

jal (Jump and link): R[rd] = pc+4;  $pc = pc + \{imm, 1b'0\}$

| 31      | 30 21     | 20      | 19 12      | 11 7 | 6 0    |

|---------|-----------|---------|------------|------|--------|

| imm[20] | imm[10:1] | imm[11] | imm[19:12] | rd   | opcode |

| 1       | 10        | 1       | 8          | 5    | 7      |

|         | offset[2  | 0:1]    |            | dest | JAL    |

| Select<br>one per<br>row | ASel Mux:<br>BSel Mux: | O "pc + 4" branch O "pc" branch O "imm" branch O "pc + 4" branch | O "alu" branch O Reg[rs1] branch O Reg[rs2] branch O "alu" branch | O * (don't care) | O * (don't |

|--------------------------|------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|------------------|------------|

| Select all that          | Datapath units         | : D Branch Comp                                                  | ☐ Imm. Gen                                                        | ☐ Load Extend    |            |

| apply                    | RegFile:               | ☐ Read Reg[rs1]                                                  | ☐ Read Reg[rs2                                                    | 2] Write Reg[rd] |            |

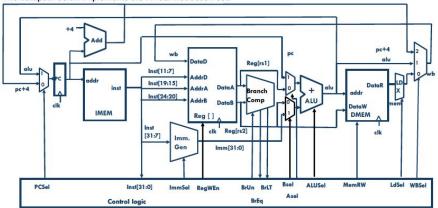

b) In the RISC-V datapath above, mark what is used by a auipc instruction.

auipc (add upper immediate to pc): R[rd] = pc+ {imm,12b'0}

| 31                 | 12 | 11 7 | 6 0    |

|--------------------|----|------|--------|

| imm[31:12]         |    | rd   | opcode |

| 20                 |    | 5    | 7      |

| U-immediate[31:12] |    | dest | AUIPC  |

| Select<br>one per<br>row | ASel Mux:<br>BSel Mux: | o "pc + 4" branch pc" branch imm" branch pc + 4" branch | O "alu" branch O Reg[rs1] branch O Reg[rs2] branch O "alu" branch |                  | O * (don't |

|--------------------------|------------------------|---------------------------------------------------------|-------------------------------------------------------------------|------------------|------------|

| Select all that          | Datapath unit          | s: Branch Comp                                          | ☐ Imm. Gen                                                        | ☐ Load Extend    |            |

| apply                    | RegFile:               | ☐ Read Reg[rs1]                                         | ☐ Read Reg[rs2                                                    | 2] Write Reg[rd] |            |

## 3) Datapathology (24 points, 25 minutes)

The datapath below implements the RV32I instruction set.

🤚 Downloads 📙 EECS151\_G... 👼 🔽 🧔 ~

a) In the RISC-V datapath above, mark what is used by a jal instruction.

jal (Jump and link): R[rd] = pc+4; pc = pc + {imm,1b'0}

| 31      | 30 2:     | 1 20    | 19 12      | 11 7 | 6 0    |

|---------|-----------|---------|------------|------|--------|

| imm[20] | imm[10:1] | imm[11] | imm[19:12] | rd   | opcode |

| 1       | 10        | 1       | 8          | 5    | 7      |

|         | offset[   | 20:11   |            | dest | JAL    |

| Select<br>one per<br>row | ASel Mux:<br>BSel Mux: | <ul><li> "pc + 4" branch</li><li> "pc" branch</li><li> "imm" branch</li><li> "pc + 4" branch</li></ul> | O "alu" branch O Reg[rs1] branch O Reg[rs2] branch O "alu" branch | Commence of the commence of th | O * (don't |

|--------------------------|------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Select all that          | Datapath units         | : D Branch Comp                                                                                        | ☐ Imm. Gen                                                        | ☐ Load Extend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

| apply                    | RegFile:               | ☐ Read Reg[rs1]                                                                                        | ☐ Read Reg[rs2                                                    | 2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| at              | 19 19 19 19         | er immediate to pc): R[r |                   |         |               |            |

|-----------------|---------------------|--------------------------|-------------------|---------|---------------|------------|

|                 | 31                  | imm[31:                  |                   | 2 11 7  | opcode        |            |

|                 | _                   | 20                       |                   | 5       | 7             |            |

|                 |                     | U-immediate[3            | 31:12]            | dest    | AUIPC         |            |

|                 |                     |                          |                   |         |               |            |

| Select          | PCSel Mux:          | "pc + 4" branch          | O "alu" branch    | O * (do | n't care)     |            |

| one per         | ASel Mux:           | O "pc" branch            | O Reg[rs1] branch | O * (do | n't care)     |            |

| row             | BSel Mux:           | O "imm" branch           | O Reg[rs2] branch | O * (do | n't care)     |            |

|                 | WBSel Mux:<br>care) | O "pc + 4" branch        | O "alu" branch    | O "me   | m" branch     | O * (don't |

| Select all that | Datapath unit       | s: Branch Comp           | Imm. Gen          | 0       | Load Extend   |            |

| apply           | RegFile:            | ☐ Read Reg[rs1]          | ☐ Read Reg[rs2    | - 0     | Write Reg[rd] |            |

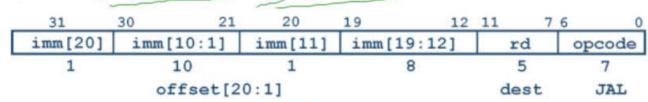

### RISC-V Datapath (FA19, Problem 3 continued)

#### 3) Datapathology (continued)

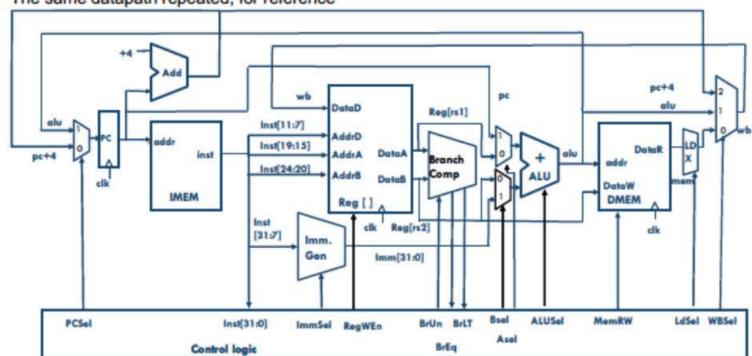

c) The same datapath repeated, for reference

Specify whether the following proposed instructions can be implemented using this datapath without modifications.

If the instruction can be implemented, specify an expression for the listed control signals, by following the example below.

| Instruction                                    | Description                                                               | Imple-<br>mentable? | Control Signals           |

|------------------------------------------------|---------------------------------------------------------------------------|---------------------|---------------------------|

| Add<br>add rd, rs1, rs2                        | R[rd] = R[rs1] + R[rs2]                                                   | Yes                 | ALUSel = Add<br>WBSel = 1 |

| Load word with add:<br>lwadd rd, rs1, rs2, imm | R[rd] =<br>M[R[rs1] + imm] + R[rs2]                                       |                     | RegWEn =<br>WBSel =       |

| beq with writeback:<br>beq rd, rs1, rs2, imm   | R[rd] = R[rs1] + R[rs2]<br>if (R[rs1] == R[rs2])<br>PC = PC + {imm, 1'b0} |                     | WBSel =<br>PCSel =        |

| PC-relative load:<br>lwpc rd, imm              | R[rd] = M[PC + imm]                                                       |                     | ASel =<br>BSel =          |

| Register offset load:<br>lwreg rd, rs1, rs2    | R[rd] = M[R[rs1] + R[rs2]]                                                |                     | ASel =<br>BSel =          |

##

#### 3) Datapathology (continued)

c) The same datapath repeated, for reference

Specify whether the following proposed instructions can be implemented using this datapath without modifications.

If the instruction can be implemented, specify an expression for the listed control signals, by following the example below.

| Instruction                                    | Description                                                               | Imple-<br>mentable? | Control Signals           |

|------------------------------------------------|---------------------------------------------------------------------------|---------------------|---------------------------|

| Add add rd, rs1, rs2                           | R[rd] = R[rs1] + R[rs2]                                                   | Yes                 | ALUSel = Add<br>WBSel = 1 |

| Load word with add:<br>lwadd rd, rs1, rs2, imm | R[rd] =<br>M[R[rs1] + imm] + R[rs2]                                       | X                   | RegWEn =<br>WBSel =       |

| beq with writeback:<br>beq rd, rs1, rs2, imm   | R[rd] = R[rs1] + R[rs2]<br>if (R[rs1] == R[rs2])<br>PC = PC + {imm, 1'b0} | X                   | WBSel =<br>PCSel =        |

| PC-relative load:<br>lwpc rd, imm              | R[rd] = M[PC + imm]                                                       |                     | ASel = PC<br>BSel = Inm   |

| Register offset load:<br>lwreg rd, rs1, rs2    | R[rd] = M[R[rs1] + R[rs2]]                                                | V                   | ASel = O                  |

### Verilog (FA19, Problem 4)

#### 4) Verilog (points, 20 minutes)

a) The following code describes a 3-bit linear-feedback shift register (LFSR), which generates a repeating pattern of pseudo-random numbers.

#### endmodule

## 4) Verilog (points, 20 minutes)

a) The following code describes a 3-bit linear-feedback shift register (LFSR), which generates a repeating pattern of pseudo-random numbers.

#### endmodule

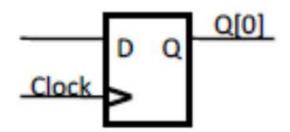

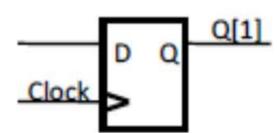

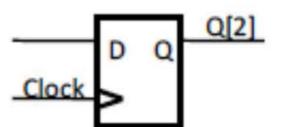

### Verilog (FA19, Problem 4)

#### 4) Verilog (points, 20 minutes)

a) The following code describes a 3-bit linear-feedback shift register (LFSR), which generates a repeating pattern of pseudo-random numbers.

```

module lfsr(

input [2:0] R,

input Load,

input Clock,

output reg [2:0] Q

);

always@ (posedge Clock)

if (Load)

Q <= R;

else Q <= {Q[1], Q[0] ^ Q[2], Q[2]};

```

#### endmodule

### Verilog (FA19, Problem 4 continued)

#### 4) Verilog (points, 20 minutes)

a) The following code describes a 3-bit linear-feedback shift register (LFSR), which generates a repeating pattern of pseudo-random numbers.

b) If the initial state of Q[2:0] is 3'b100, write the outputs that correspond to the first 8 cycles:

| Cycle | Q[2:0] |

|-------|--------|

| 0     | 100    |

| 1     |        |

| 2     | 103    |

| 3     | S      |

| 4     | Í      |

| 5     | 33     |

| 6     |        |

| 7     |        |

## Verilog (FA19, Problem 4 Continued)

## 4) Verilog (points, 20 minutes)

a) The following code describes a 3-bit linear-feedback shift register (LFSR), which generates a repeating pattern of pseudo-random numbers.

b) If the initial state of Q[2:0] is 3'b100, write the outputs that correspond to the first 8 cycles:

| Cycle | Q[2:0] |

|-------|--------|

| 0     | 100    |

| 1     | 011    |

| 2     | /10    |

| 3     | (1)    |

| 4     |        |

| 5     | 201    |

| 6     | 010    |

| 7     | 100    |

### Verilog (FA19, Problem 4 continued)

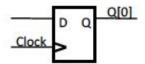

#### 4) Verilog (continued)

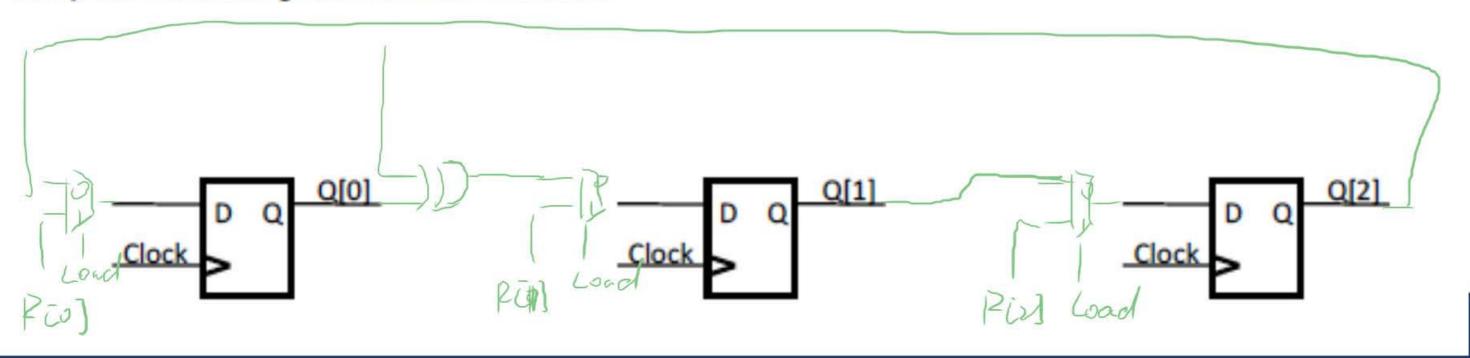

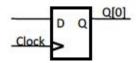

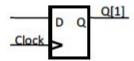

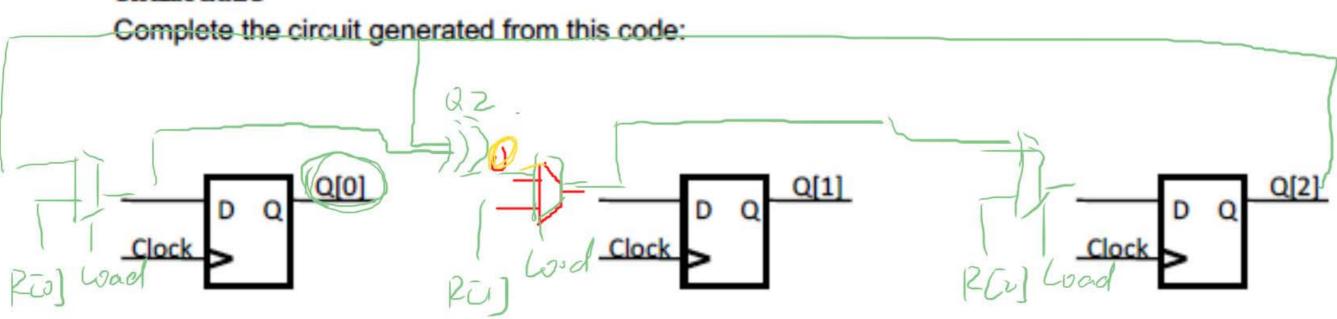

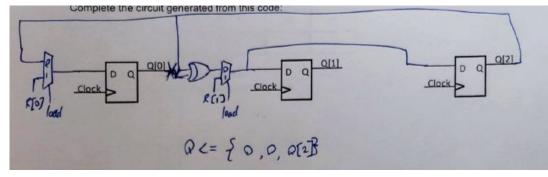

c) Similar code is shown below: module lfsr(R, Load, Clock, Q) ; input [2:0] R; input Load, Clock; output reg [2:0] Q; always@ (posedge Clock) if (Load) Q <= R; else begin Q[0] = Q[2]; $Q[1] = Q[0] ^ Q[2] ;$ Q[2] = Q[1];end endmodule Complete the circuit generated from this code:

UNIVERSITY OF CALIFORNIA

##

## 4) Verilog (continued)

Q = {0,0,Q[2]}

#### endmodule

🔽 Iru cache - ... 💘 Jalopnik | ... 🙎 Midterm 1 ... 🎅 Spotify Pre... 🦀 Slack | Zhe... 🤵 Signal

21

### Verilog (FA19, Problem 4 continued)

#### 4) Verilog (continued)

endmodule

Complete the circuit generated from this code:

UNIVERSITY OF CALIFORNIA

### Verilog (FA19, Problem 4 continued)

#### 4) Verilog (continued)

c) Similar code is shown below:

```

module lfsr(R, Load, Clock, Q) ;

input [2:0] R;

input Load, Clock;

output reg [2:0] Q;

always@ (posedge Clock)

if |(Load)

Q <= R;

else begin

Q[0] = Q[2];

Q[1] = Q[0] ^ Q[2] ;

Q[2] = Q[1];

end</pre>

```

endmodule

Complete the circuit generated from this code:

d) If the R[2:0] value of 3'b100 is loaded initially, write the outputs that correspond to the first 8 cycles:

| Cycle | Q[2:0] |

|-------|--------|

| 0     | 100    |

| 1     |        |

| 2     |        |

| 3     |        |

| 4     |        |

| 5     |        |

| 6     |        |

| 7     |        |

## Verilog (FA19, Problem 4 Continued)

## 4) Verilog (continued)

d) If the R[2:0] value of 3'b100 is loaded initially, write the outputs that correspond to the first 8 cycles:

| Cycle | Q[2:0] |

|-------|--------|

| 0     | 100    |

| 1     | 221    |

| 2     | 0 0 0  |

| 3     | 200    |

| 4     | 000    |

| 5     | 000    |

| 6     | 000    |

| 7     | 000    |

Q = 10.0.Q[2]

endmodule