#### EECS 151/251A Homework 1

Due Friday, Sept 11<sup>th</sup>, 2020

#### Problem 1: Dennard Scaling [4 pts]

Imagine that we still live in the world of ideal Dennard scaling. You designed a brilliant laptop microprocessor that runs at 4GHz, but dissipates 45W. What would be its power and performance in the next technology node, with features that are scaled by a factor of 0.8?

## Problem 2: Wafer Yield [4 pts]

You want to fabricate a new chip using TSMC's 5nm node. You will use 600 mm wafers with  $\alpha=3$  and a defect per unit area of  $0.001\,/\mathrm{mm^2}$ . The die area is  $1\,\mathrm{cm^2}$  and the wafer cost is \$80k. What is your die yield and die cost?

#### Problem 3: Power and Energy [6 pts]

- (a) Briefly explain why as a designer you would be concerned with the following. Give 2 reasons each. Think about the applications of your design. [1 pt each]

- Energy Consumption

- Power Consumption

- (b) You find yourself are in charge of designing a battery and charger for a new laptop that dissipates 50W. If you expect this laptop to have 9 hours of battery life, how much energy (in Joules) must the battery hold at a full charge? [2 pts]

- (c) To ensure that users can use the laptop while it charges, you decide that the laptop should charge from 0 to 100% in 2 hours if it is in use. How much power should the charger be able to supply for this to be possible? [2 pts]

Version: 1 - 2020-09-02 00:55:49-06:00

### Problem 4. Boolean Logic [6 pts]

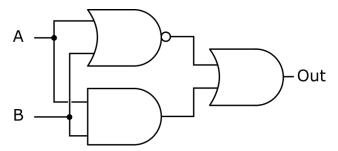

(a) For the digital logic circuit shown below, give the truth table. What is the equivalent boolean operation of this circuit? [3 pts]

(b) By inspection, draw the equivalent circuit for the given truth table using simple logic gates. You should not use more than 4 logic gates. [3 pts]

| A | В | $\mathbf{C}$ | Out |

|---|---|--------------|-----|

| 0 | 0 | 0            | 0   |

| 0 | 0 | 1            | 0   |

| 0 | 1 | 0            | 0   |

| 0 | 1 | 1            | 1   |

| 1 | 0 | 0            | 0   |

| 1 | 0 | 1            | 0   |

| 1 | 1 | 0            | 1   |

| 1 | 1 | 1            | 1   |

# Problem 5. Noise Margins [5 pts]

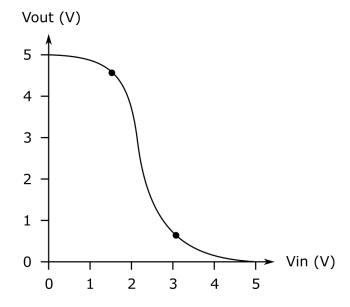

Estimate  $V_{OH}$ ,  $V_{IH}$ ,  $V_{OL}$ ,  $V_{IL}$ , and the noise margins for the voltage transfer characteristic shown below. The dots along the line show roughly where the slope = -1.

Version: 1 - 2020-09-02 00:55:49-06:00