## EECS 151/251A Homework 7

Due Friday, Oct 30<sup>th</sup>, 2020

## Problem 1: RC Delay and Logical Effort Basics

Take a CMOS inverter in a process where  $\gamma = \frac{C_d}{C_g}$  ( $\gamma = 1$  in lecture), and the PMOS effective on-resistance is equal to K times that of the NMOS (i.e.  $R_p = K \cdot R_n$ , K = 1 in lecture) for minimally sized transistors.

- (a) Draw the inverter at the transistor-level and size each FET for equal pull-up and pull-down strength. Assume the NMOS is of size '1', normalized to the minimum width of the process.

- (b) Write down the delay of this unloaded inverter using RC time constants in terms of  $\gamma$ ,  $R_n$ , and  $C_g$ . Call this delay  $t_{parasitic}$ . Assume input step transitions.

- (c) Now let the inverter have a load of  $C_L$  attached to its output. Call the quantity  $f = C_L/C_{in}$ . Write the delay of the inverter in terms of  $\gamma$ ,  $t_{parasitic}$ , and f.

- (d) Recall that the gate delay for any CMOS gate can be expressed as:

$$t_{p,gate} = \tau_{inv}(p + f \cdot LE)$$

where  $\tau_{inv}$  is a process constant, p is the intrinsic delay of the gate, and LE is the logical effort of the gate.

What are these values for an inverter?

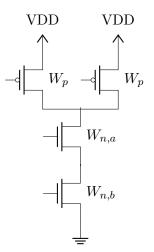

(e) Take the following sizing of a NAND2 gate. What is  $W_p$  for inverter equivalent delay? Prove that  $W_{n,a} = W_{n,b} = 2$  so the gate has equivalent self-loaded delay to an inverter and consumes minimal area.

- (f) Find the logical effort of this NAND2 gate for both inputs. What happens to the LE as K increases, and why does it make intuitive sense?

- (g) What is the intrinsic delay of a NAND2 gate (i.e. find  $p_{NAND2}$ )? Make the assumption that K = 2.

## **Problem 2: Complementary CMOS**

(a) Design a complex CMOS logic gate that implements the function below:

$$Y = \overline{(A+B)} \cdot \overline{CD} \tag{1}$$

- (b) You are using a modern technology in which a minimum sized inverter has PMOS with width 1 and NMOS with width 1 ( $R_{ON,PMOS} = R_{ON,NMOS}$ ). Size your design in (a) and try to minimize the overall area. Assume the total area is proportional to the sum of transistors' width.

- (c) Calculate the logic effort for input A and C with the assumptions in (b).

## Problem 3: Path delay with logical effort

For this problem, assume you have a reference inverter with  $W_P = W_N = 1$ . This technology has  $\gamma = 1.2$

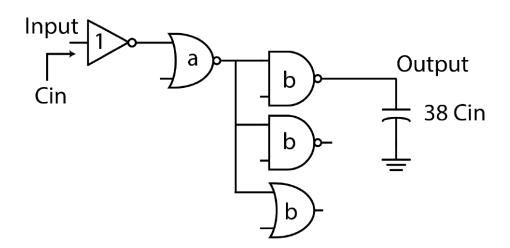

- (a) Determine the path effort from input to output, and optimal stage effort for the circuit shown above. Note that a and b are the input capacitance of each input.

- (b) Find the optimum a and b in terms of  $C_i n$  for minimum delay in the critical path (input to output).