## EECS 151/251A SP2022 Discussion 10

GSI: DIMA NIKIFOROV, YIKUAN CHEN

## Agenda

- Latches

- Flip-Flops

- SRAMs

## Latches

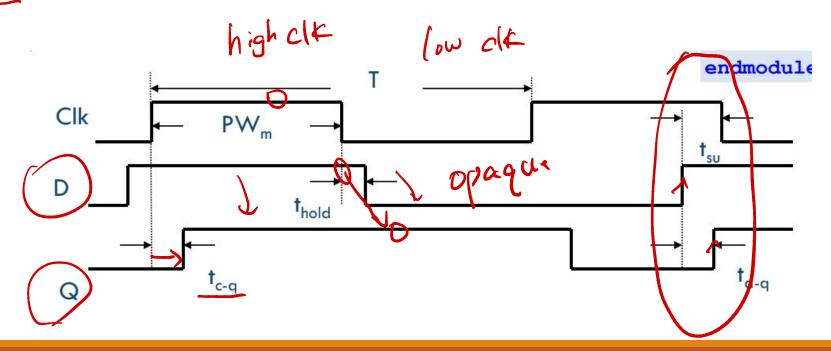

## Latch Timing

- A positive latch is **transparent** (q = d) when the **clock is high** and **opaque** (q = d), sampled at negedge clock) when the **clock is low**

- $\mathbf{t}_{d\rightarrow q}$ : delay from d to q when the latch is transparent

- $t_{clk->q}$ : delay from the rising clock edge to d propagating to q

EECS 151/251A DISCUSSION 9

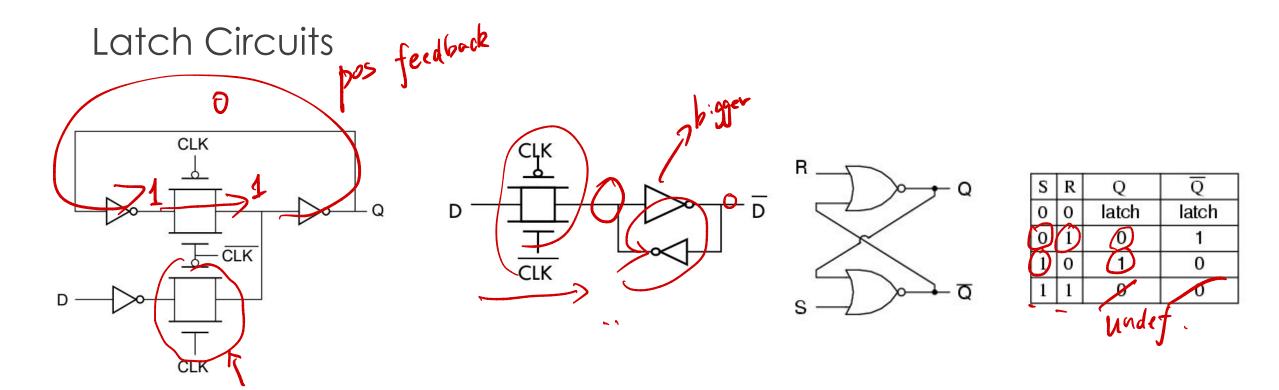

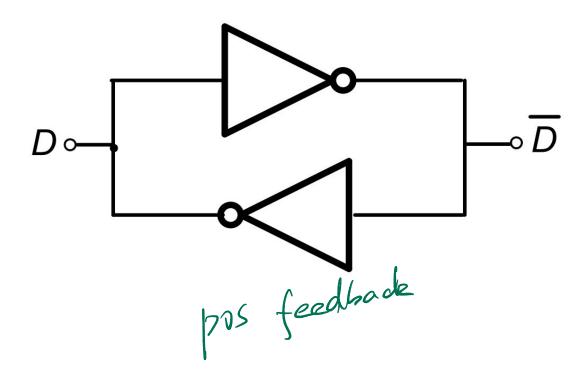

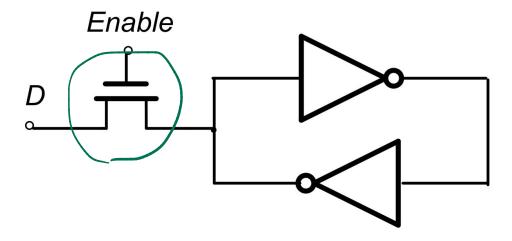

'Feedback-breaking' latch Transparent high

'State-forcing' latch Transparent low SR latch Common interview question

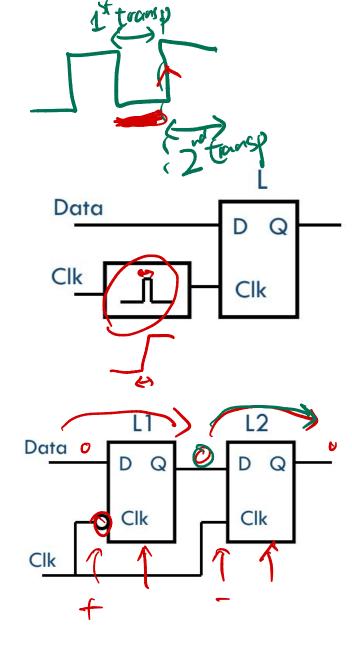

## Building a Flip-Flop from Latches

#### Clock pulsed latch

- Latch becomes transparent for the pulse duration only, then holds data

- Not common anymore, sometimes used in high performance circuits

- Positive hold time

#### Pair of latches – edge triggered (posedge clk!!!)

- Commonly used technique

- L2 holds output data stable when clock is high.

- Negative hold time

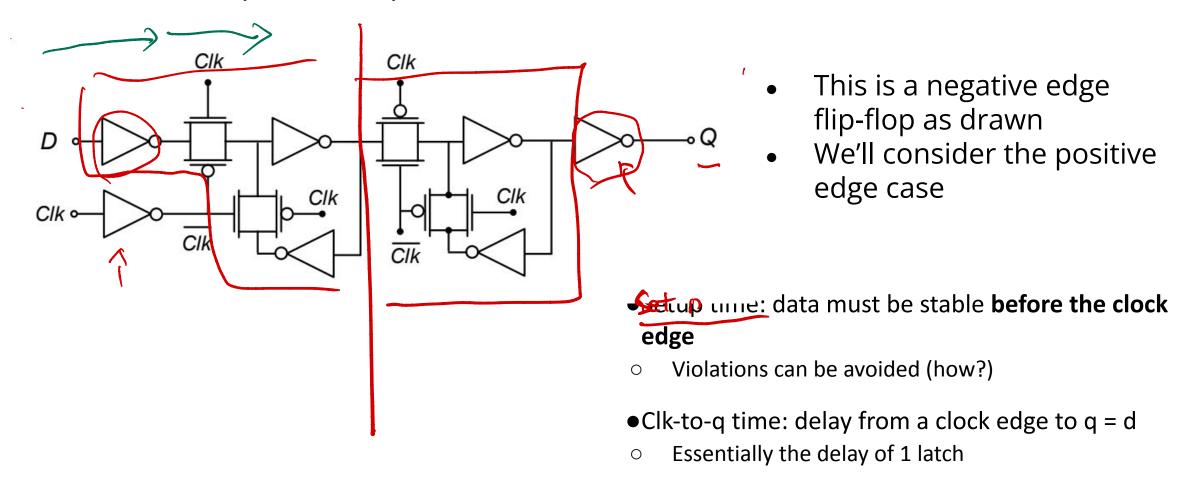

# Flip-Flops

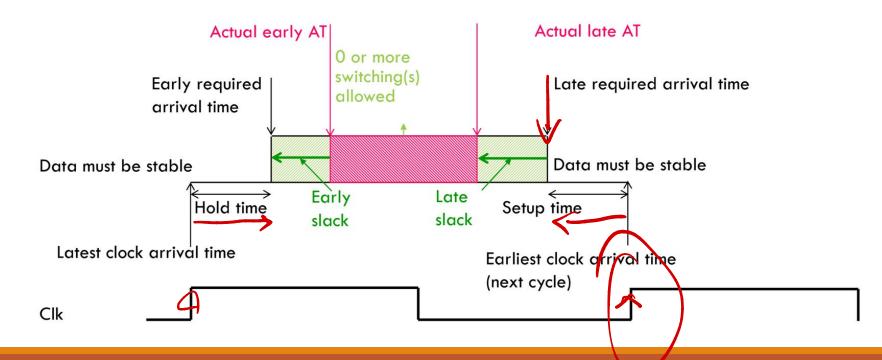

### Hold, Setup, clk->q Time

EECS 151/251A DISCUSSION 9

## Path Timing Constraints

- Setup constraint:  $T_{clk} > t_{clk->q} + t_{logic,max} + t_{setup}$

- The clock period must be greater than the delay of the critical path

- Hold constraint:  $t_{hold} < t_{clk->q} + t_{logic,min}$

- The minimum logic delay must be greater than the hold time

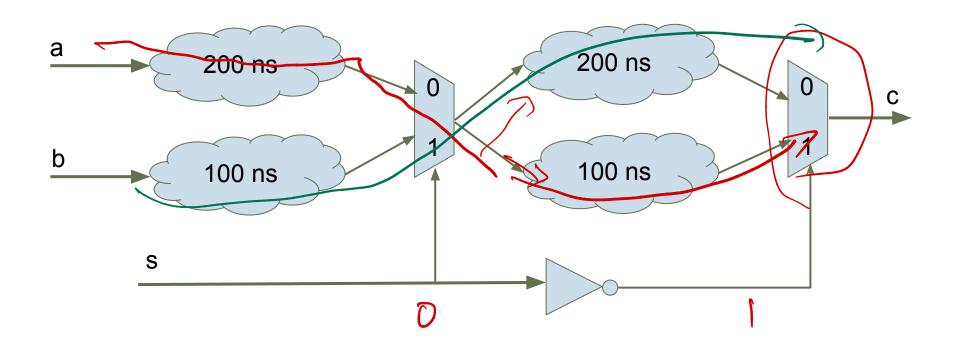

#### False Paths

- Be careful about finding the critical path by statically adding up delays

- Some paths may not be exercised based on logic expressions

- Here, the critical path is not 400ns. What is it?

EECS 151/251A DISCUSSION 9 10

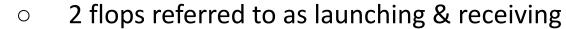

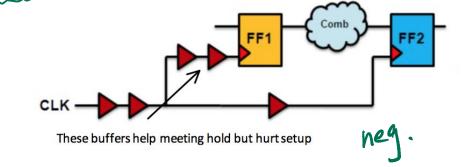

#### Clock Skew

Skew: the deterministic clock arrival time difference between 2 flops

Positive = clock to receiving arrives later than to launching

Negative = clock to receiving arrives **earlier** than to New timing equations: tseep < Tak - tag - tag - tag -

Negative skew hurts setup margin

These buffers help meeting setup but hurt hold

EECS 151/251A DISCUSSION 9

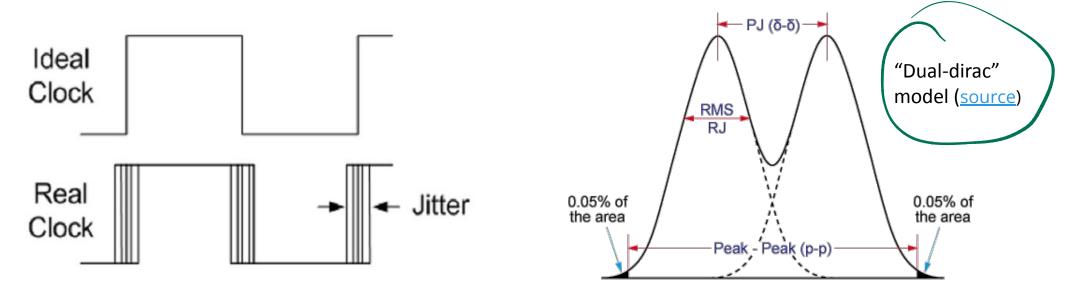

#### Clock Jitter

- Jitter is the **non-deterministic** difference in clock arrival times

- Types: period & cycle-to-cycle

- Can be treated like skew in timing calculations

- Assume worst case jitter in the unfavorable direction for timing calculation

- Lump jitter of both the launching and receiving FFs into an equivalent skew

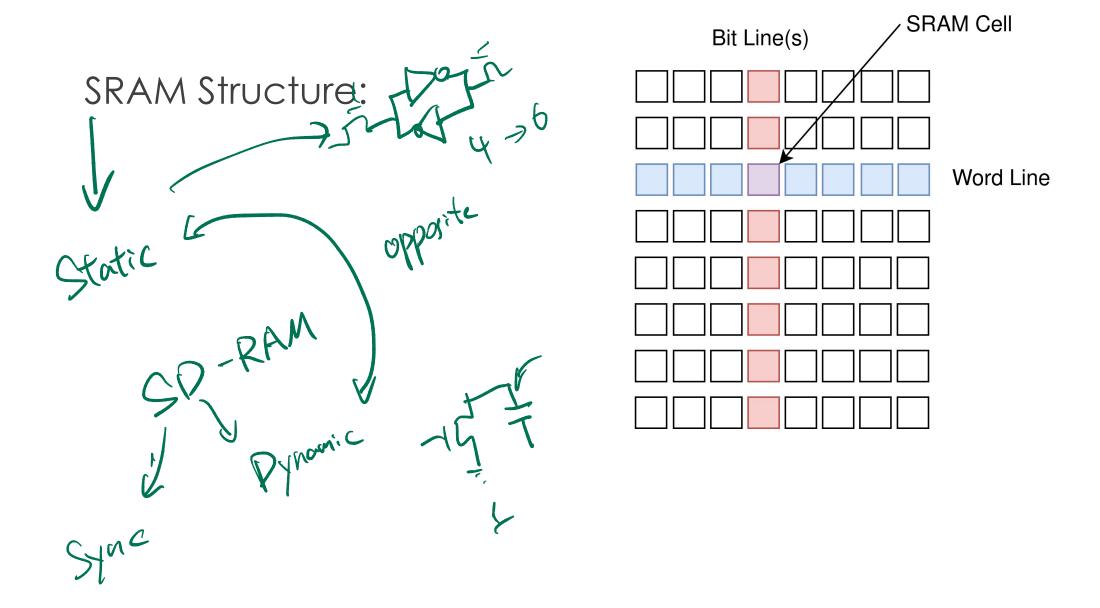

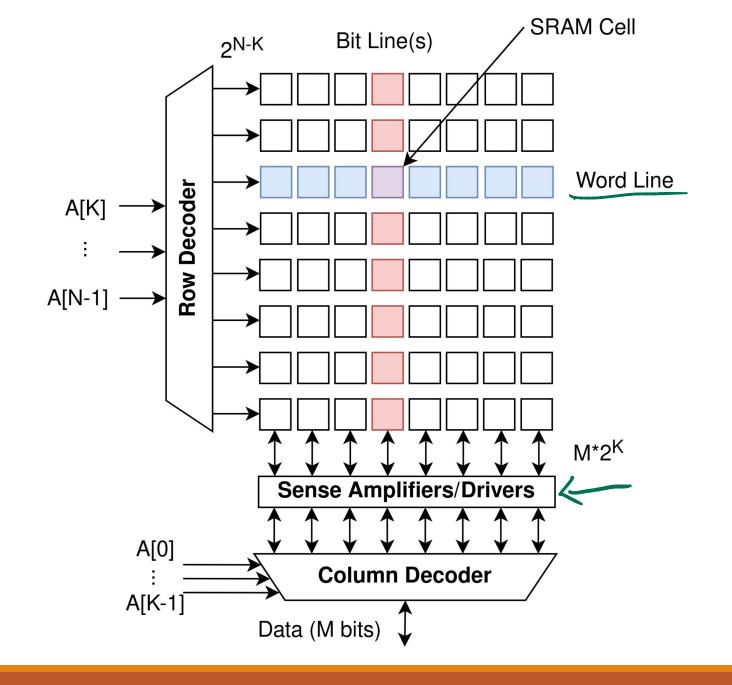

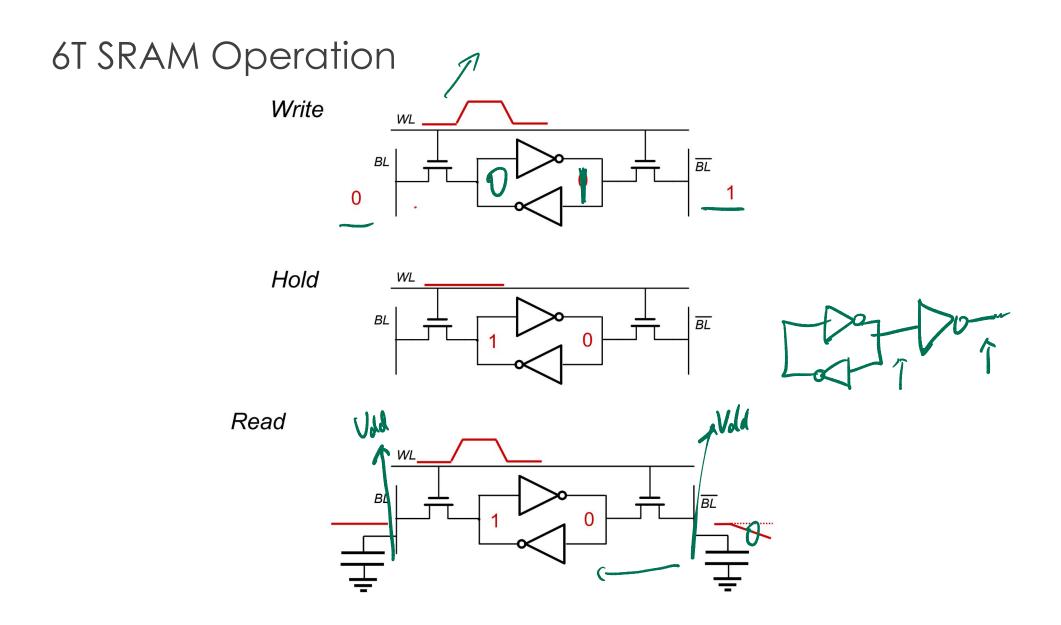

## SRAMs

### SRAM Structure:

## SRAM: Basic Static Memory Component:

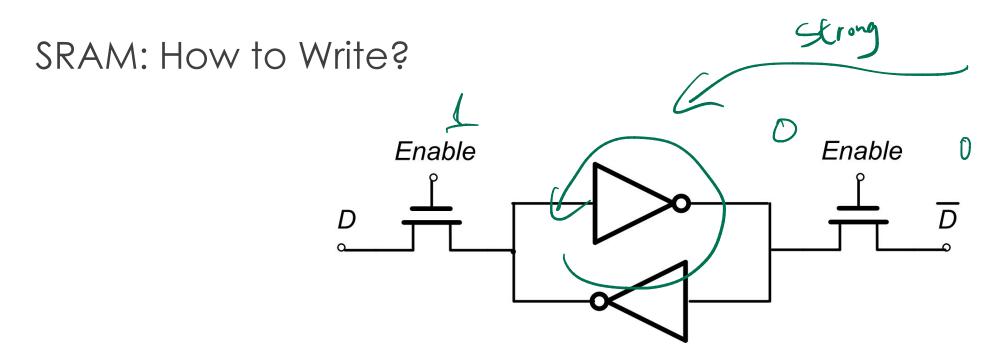

#### SRAM: How to Write?

- Challenge: How do you overpower the feedback loop?

- Challenge: Writing 0 vs writing 1?

- **Challenge:** How do you overpower the feedback loop?

- Challenge: Writing 0 vs writing 1?

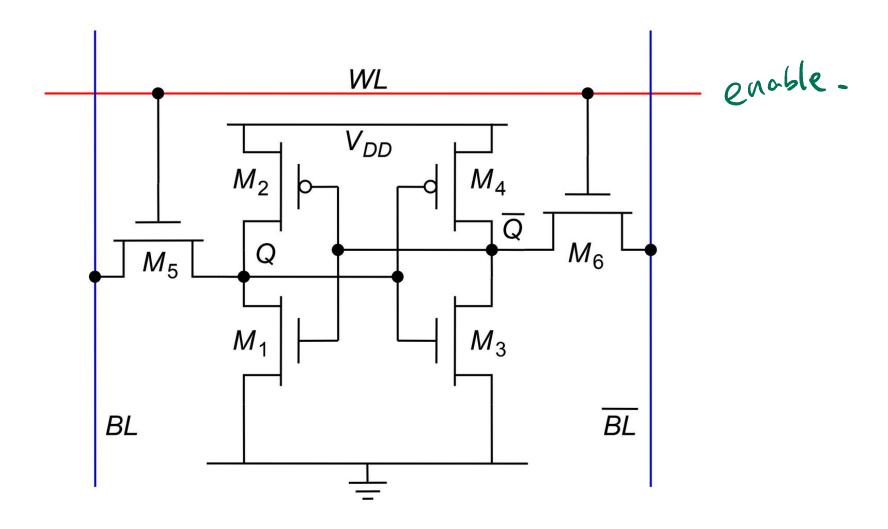

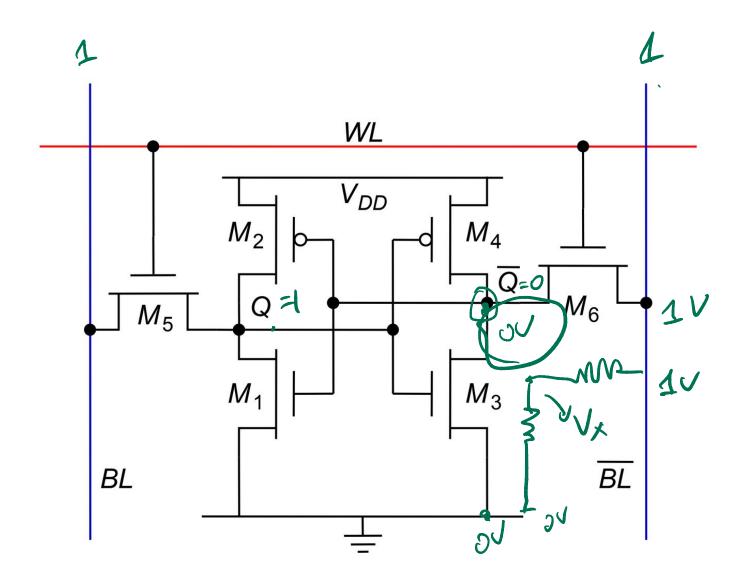

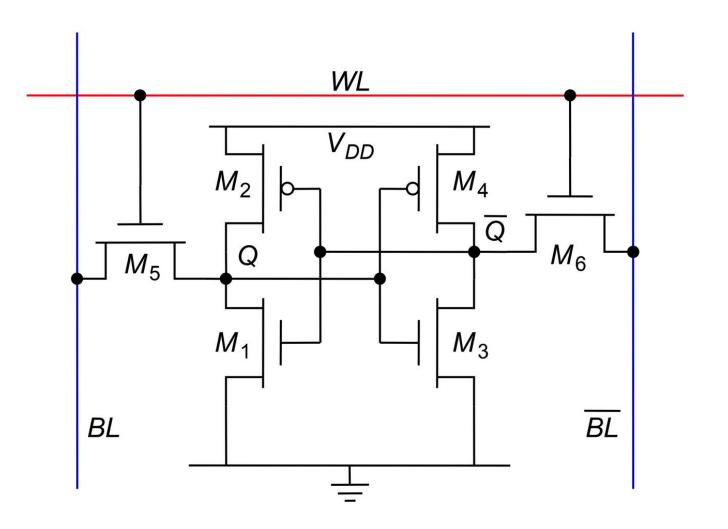

## 6T SRAM Cell

## 6T SRAM Cell Sizing

• Read Sizing:

• Write Sizing:

#### Dual Port SRAM Modifications: 1 Read 1 Write

What additional logic is needed?

## Questions?