# Welcome to EECS 16A!

**Designing Information Devices and Systems I**

#### Ana Claudia Arias and Miki Lustig Fall 2021

Module 2 Lecture 2 Introduction to Circuit Analysis (Note 12)

#### Last Class (0203)...

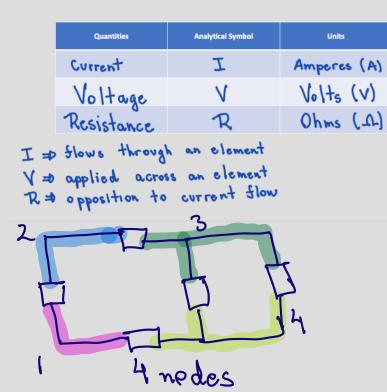

|    | Quantities                                       | Analytical Symbol | Units       |

|----|--------------------------------------------------|-------------------|-------------|

|    | Current                                          | I                 | Amperes (A) |

|    | Voltage                                          | V                 | Volts (V)   |

|    | Resistance                                       | R                 | Ohms (II)   |

| V= | Slows through<br>applied across<br>opposition to |                   |             |

Electronic Materials

· Semiconductor

· Conductors

· Insulators

\* Charge ≠ Can be either positive or negative; basic element of eletric tlow. Unit: Covlomb [C]

\* Current ⇒ Net amount of charge that passes through some cross-section area over a period of time.

[A] → I = d@ [C]

#### Last Class (0203)...

· First operator!

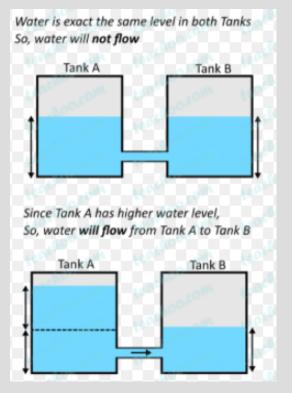

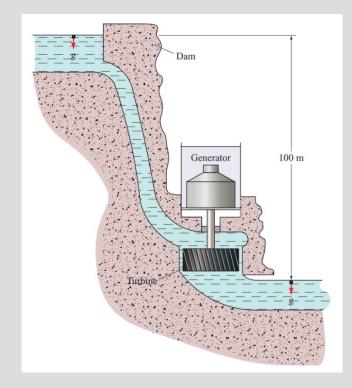

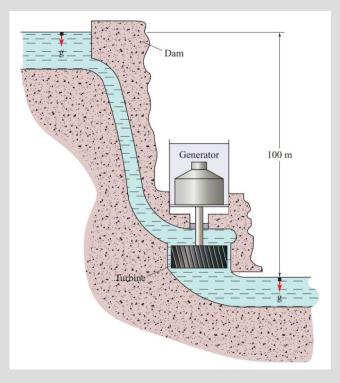

## **Potential Energy**

#### **Potential and Voltage**

#### Electronic Devices depend on movement of charges

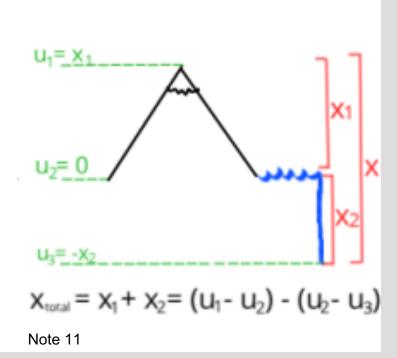

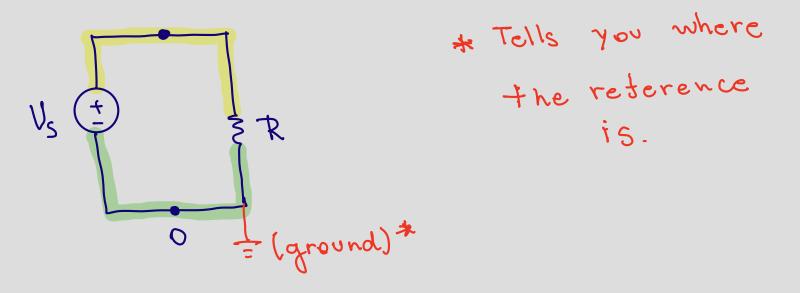

We always need to define a reference for potentials. Ground = 0

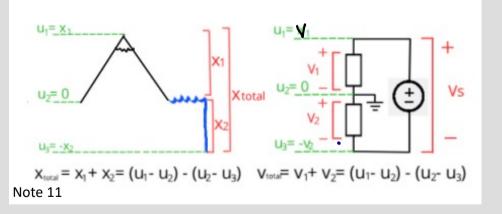

$V_2, V_3$ potentials  $V_1 = U_1 - U_2$  $V_2 = U_2 - U_3$  $= V_1 + V_2$

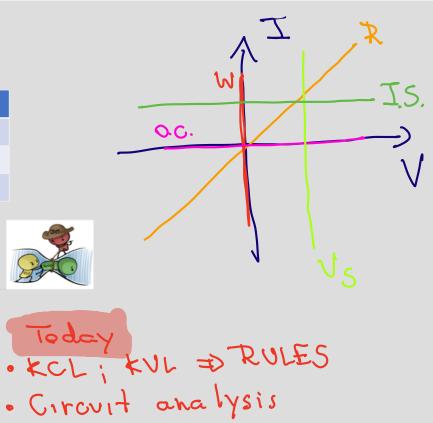

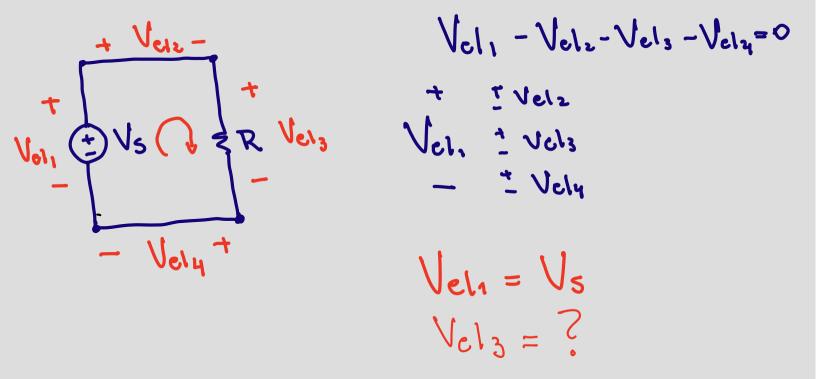

#### Rules for circuit analysis: Kirchoff's Voltage Law (KVL)

Sum of Voltages across the elements in a loop equal zero

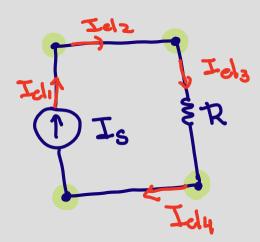

#### Rules for circuit analysis: Kirchoff's Current Law (KCL)

The current flowing into any junction must equal the current flowing out

Iel, = Iclz Jolz = Jolz Ida = Ida Joly = John

Iels + Iak = Iel:

#### Rules for circuit analysis: KCL within the element

The current flowing into any junction must equal the current flowing out

Pick a reference node and label it as 0 potential. All voltages measured relative to this node.

Label all branch currents with  $I_m$ Arbitrarily pick directions of  $I_m$  $[I_1 ... I_k]$

Add signs + and – element voltages to each element following the passive sign convention

Use KCL to fill as many rows of A as possible (linear independence) # Nodes -1 = N-1

Use current-voltage relationships for each element to fill the rest of the A matrix

Voltage Element = -Vs 5  $V_{el} = 0 - U_{l}$  $V_{2}$  $V_1 = V_1 = V_S$  $\begin{vmatrix} -1 & 0 & J_1 \\ 0 & 0 & I & J_2 \end{vmatrix}^{-1}$   $0 & R - I & U_1$ Resistor  $Vel_2 = I_2 \cdot R$ Vel2 - U, - D = U,  $U_1 = V_5$ I2 =  $U_1 = I_2 \cdot R$  $\Sigma_1 = \sqrt{c}$  $I_2 \cdot R - U_1 = O$

# Node Voltage Analysis - Voltage Divider, make circuit (Operator) - analysis faster

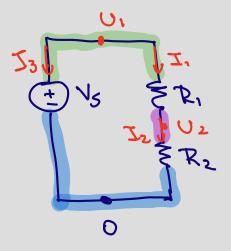

, Step 1 – Pick a node and label it as ground

#### Node Voltage Analysis – Voltage Divider

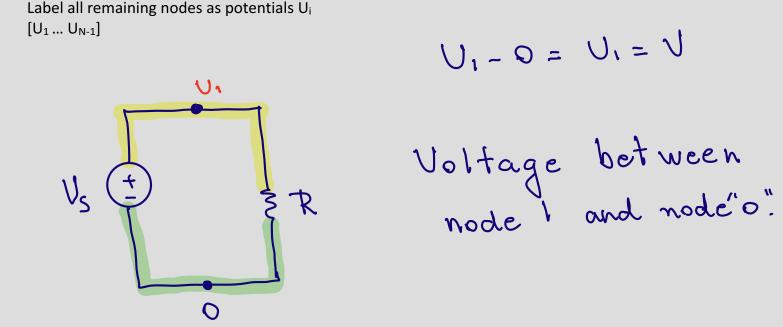

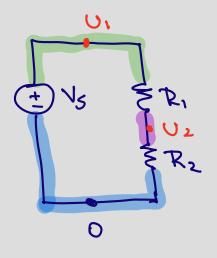

Step 2 – Label all remaining nodes as some potential U<sub>i</sub>.

#### Node Voltage Analysis – Voltage Divider

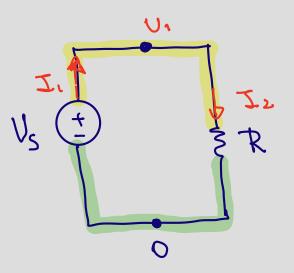

Step 3 – Label the current through every non-wire element in the circuit with  $I_n$ .

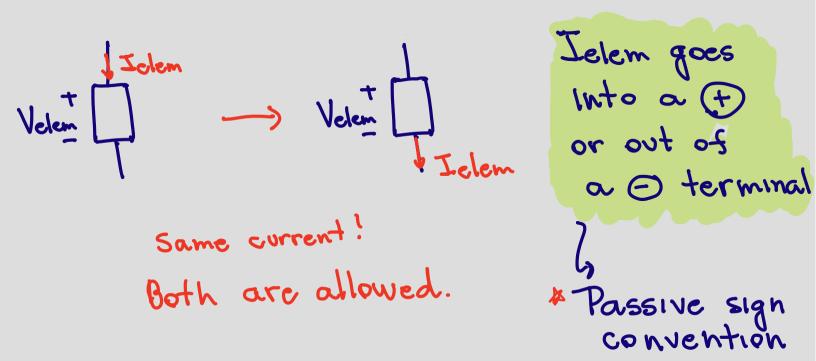

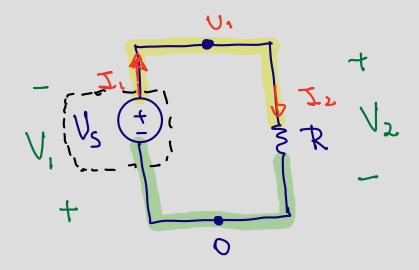

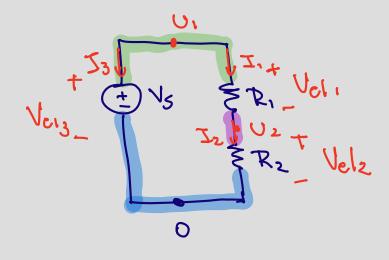

# Node Voltage Analysis – Voltage Divider Step 4 – Add +/- labels on each non-wire element, following the passive sign convention.

\* Importan Passive sign convention: the current enters at the positive terminal and exits are the negative terminal.

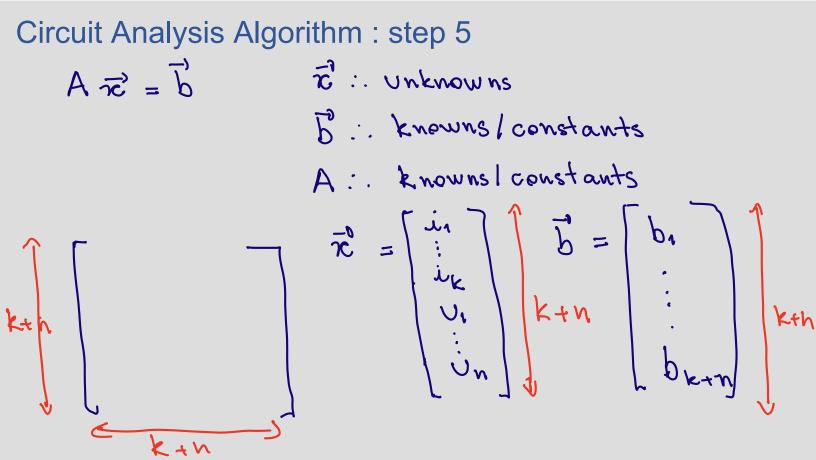

#### Node Voltage Analysis – Voltage Divider $A\vec{x} = \vec{b}$

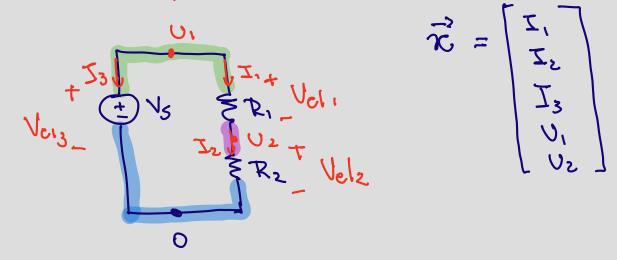

Step 5 – Set up the relationship ⋪ consists of the unknown currents and potentials.

Identify the unknowns.

Passive sign convention: the current enters at the positive terminal and exits are the negative terminal.

#### Node Voltage Analysis – Voltage Divider

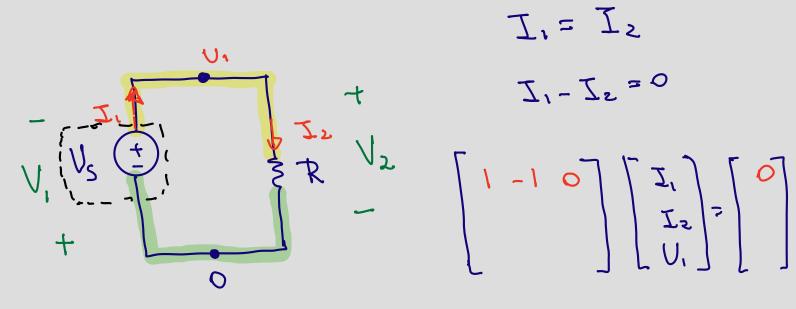

Step 6 – Use KCL to fill in as many linearly independent rows in  $\mathbf{A}$  and  $\mathbf{b}$

- For  $U_1 \not\supset O = I_1 + I_3$  (1) For  $U_2 \not\supset J_1 = J_2$

- $I_1 I_2 = 0$  (2)

KUL: the current flowing into a junction must equal the current flowing out of that junction.

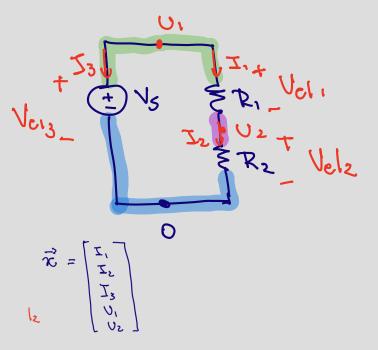

#### Node Voltage Analysis – Voltage Divider

Step 7 - Use the IV relationships of each of the non-wire elements to fill in the remaining rows of A and

Voltage Def. = Q (1) =0 (2) Veh= U1-U2 Ver3 Vel2 = U2-0 = U2  $Vel_3 = U_1 - O = U_1$ Substitution:  $E_{1}$ :  $U_{1} - U_{2} = R_{1}I_{1} \Rightarrow R_{1}I_{1} - U_{1} + V_{2} = O(3)$ Element JV = Elz: Uz = R2I2 = R2I2-U2=0 (4) Vel, = R.I. Velz=R2IL  $E_{13}$ :  $U_1 = V_5$  (5) Vels = Vs

#### Node Voltage Analysis – Voltage Divider Step 8 – Solve the system of equations to determine values of unknown variables. $\underline{T}_1 + \underline{T}_3 = 0 \quad (1)$ -J, + J2 =0 (2) O $\mathbf{O}$ $R_{1} - U_{1} + U_{2} = 0$ (3) 000 11-00 $R_2I_2 - U_2 = 0$ (4) Ri R200-1 0 U, = V3 (5) $\Sigma_1 =$ 13 J2= 2 K2 Vi= VS $U_2 =$ ah $\alpha$ , 21

### Electrical Circuit Analysis Algorithm (tool)

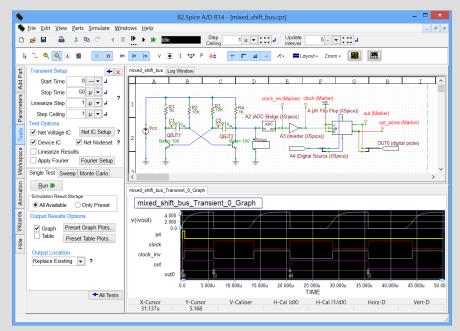

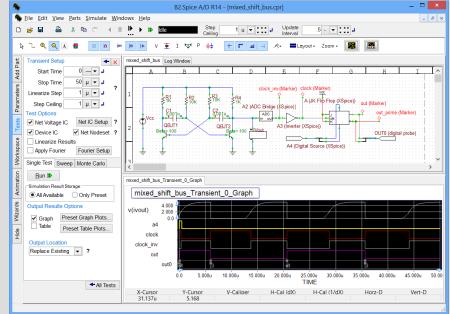

SPICE (Simulation Program with Integrated Circuit Emphasis): started as a student project at Berkeley!

Now the basis for open-source electronic circuit simulation, to design and model device characteristics and check circuit boards

Prof. Alberto L. Sangiovanni-Vincentelli

#### Electrical Circuit Analysis Algorithm (tool)