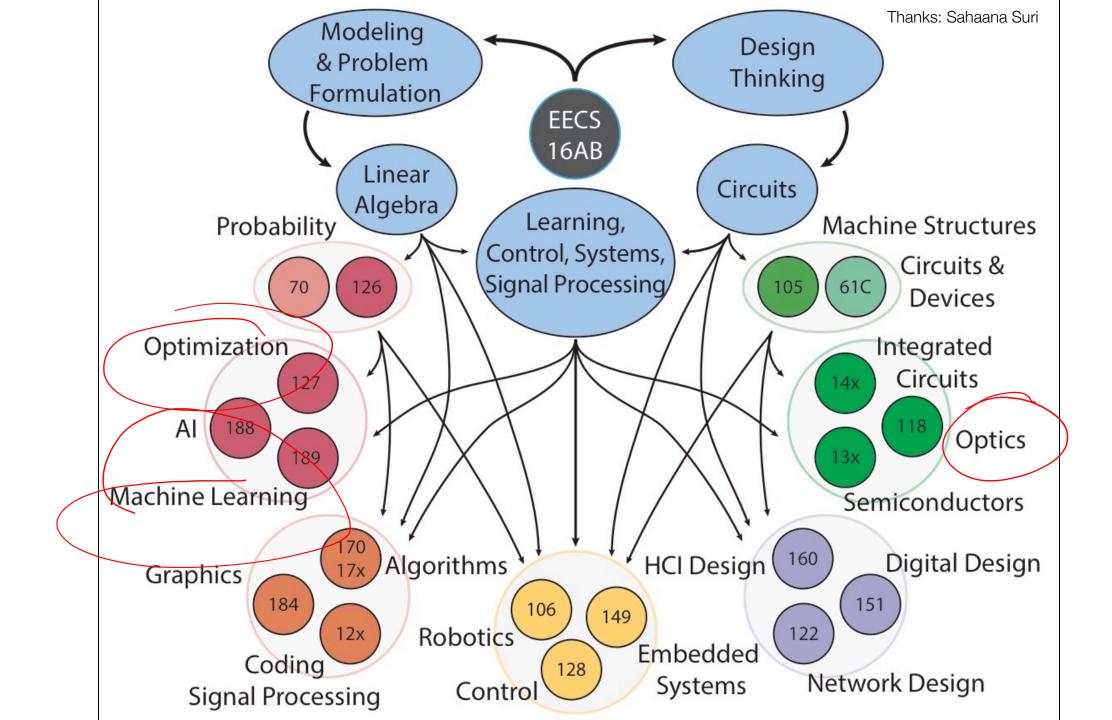

# Welcome to EECS 16A!

Designing Information Devices and Systems I

Prof. Laura Waller Prof. Rikky Muller Spring 2023

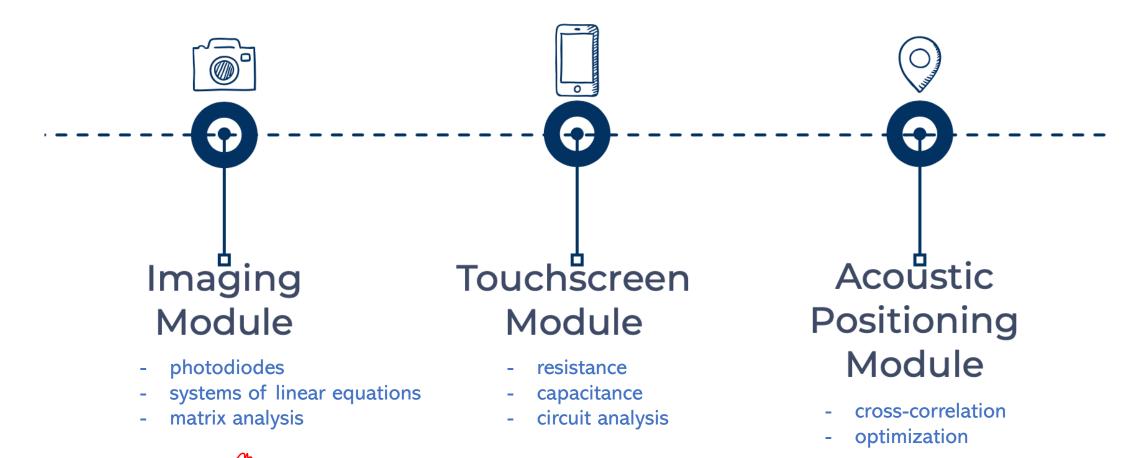

## all of these extract information from the real world and interact with it;

### we will learn how to design and analyze such devices and systems

### Instructors

Prof. Laura Waller waller@berkeley.edu

Prof. Rikky Muller rikky@berkeley.edu

#### Office Hours: 11am Wednesdays, Cory Hall room 504 (starts next week)

• Other contributors to 16: Vladimir Stojanovic, Anant Sahai, Gireeja Ranade, Ali Niknejad, Claire Tomlin, Michel Maharbiz, Miki Lustig, Vivek Subramanian, Thomas Courtade, Babak Ayazifar, Ana Arias

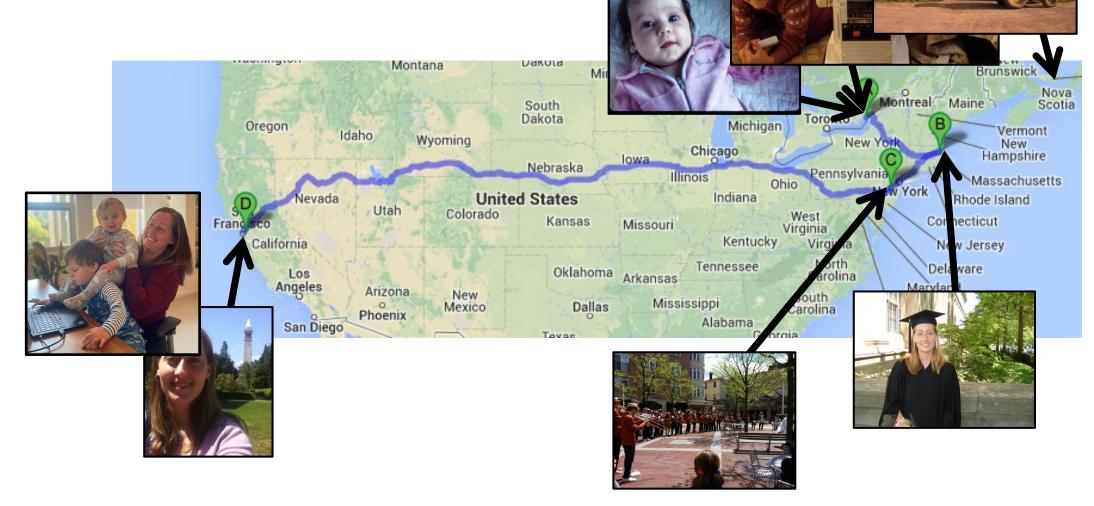

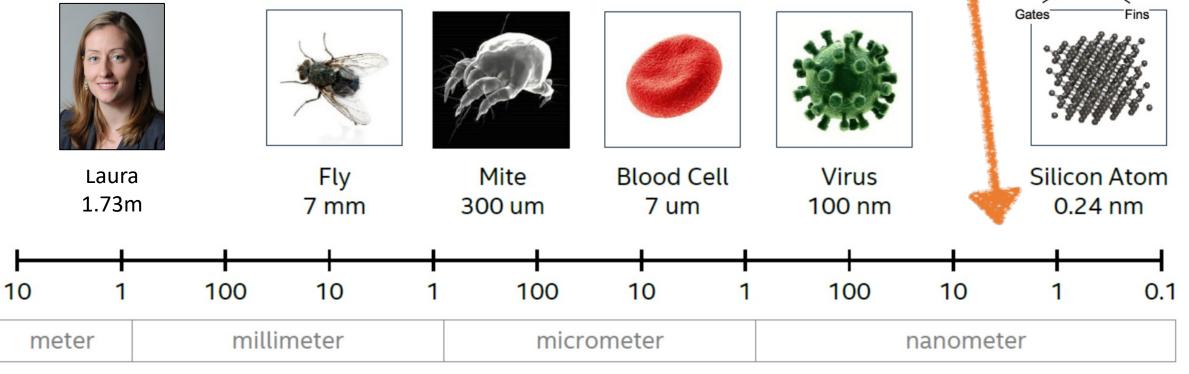

### Laura: About me

- PhD 2010, M.Eng 2005, BS 2004 EECS, MIT

- Lecturer in Physics, Postdoc in EE, Princeton 2010-2012

- Professor, UC Berkeley 2012-2050?

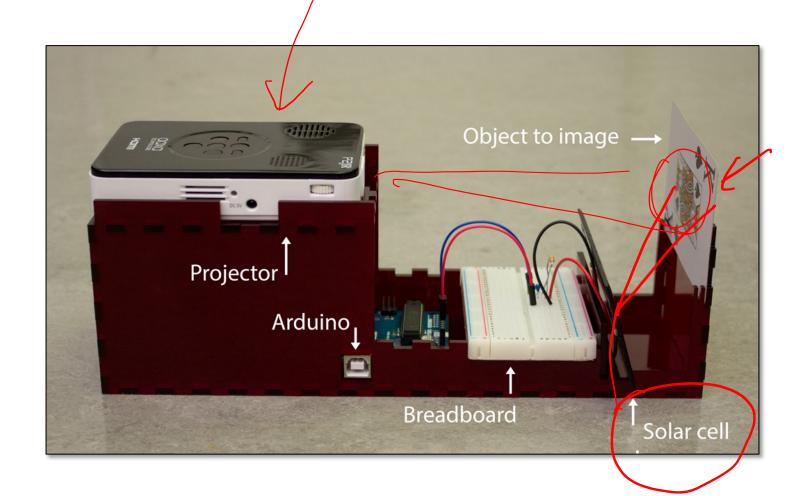

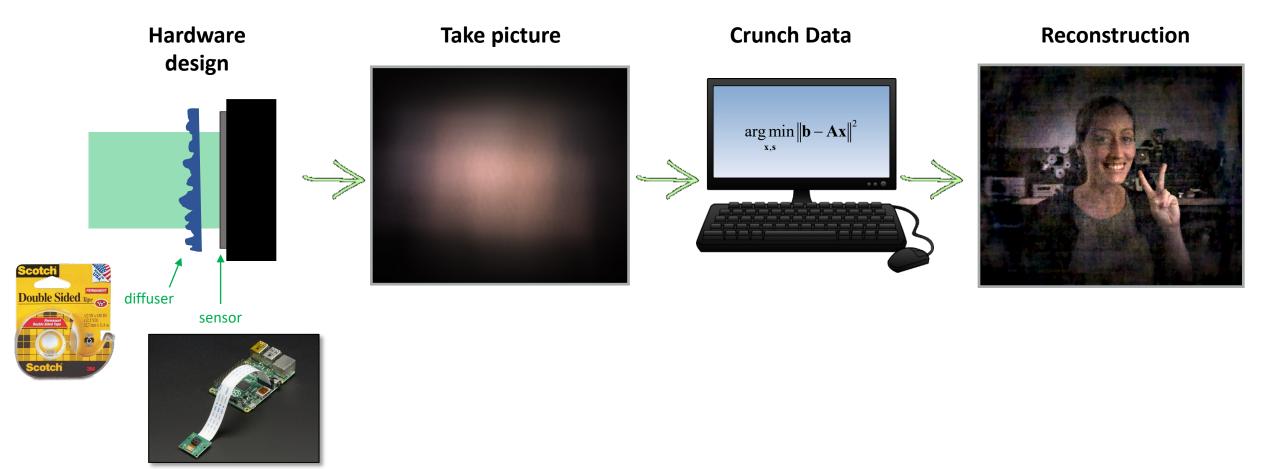

## Laura: Research in Computational Imaging

https://waller-lab.github.io/DiffuserCam/tutorial.html

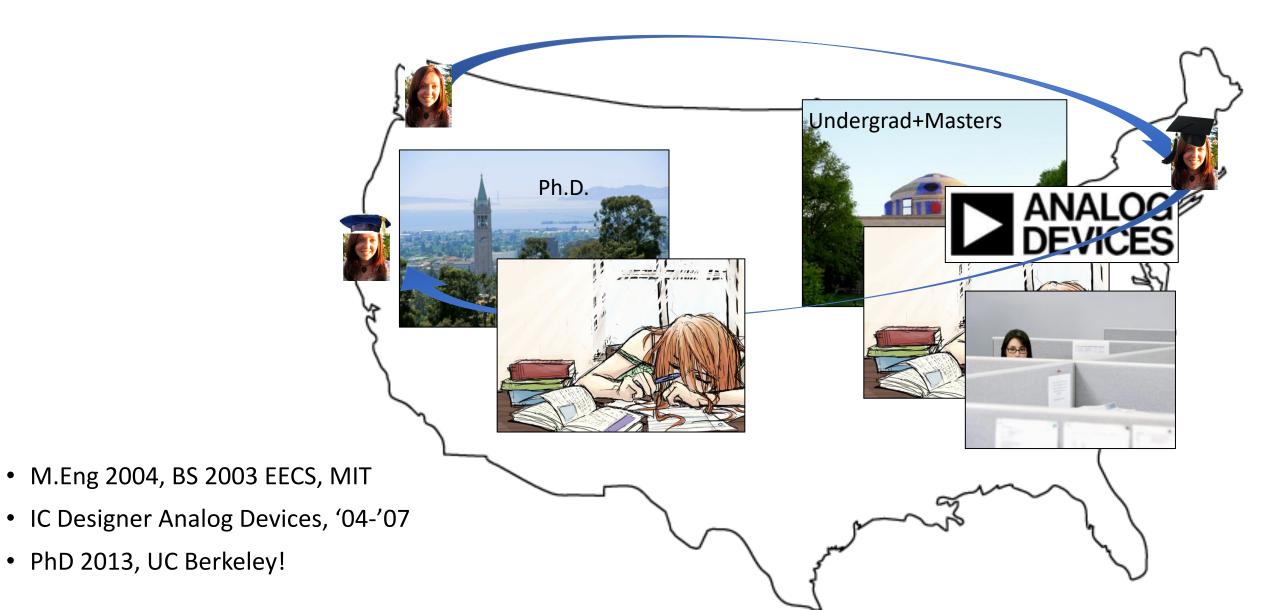

### Rikky: About me

# Rikky: About me 2 00 • Lecturer/Postdoc University of Melbourne • Startup founder: Cortera Neurotechnologies (acq. 2019) • Professor since 2016 **CORTERA** neurotechnologie

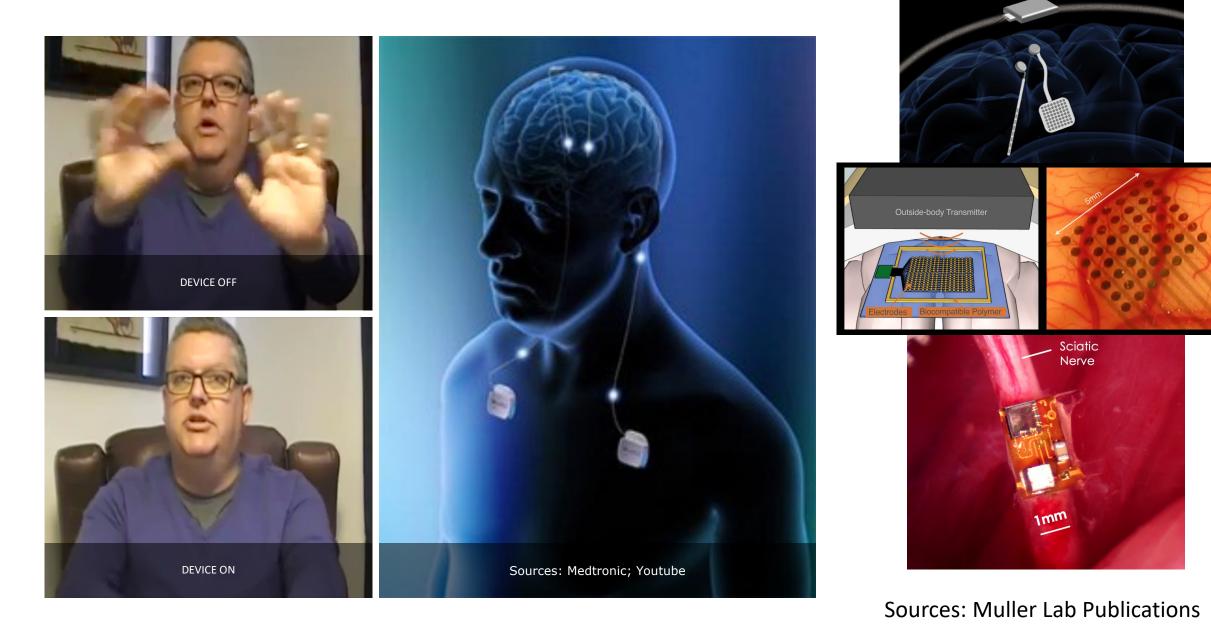

### Rikky: Research in Neurotechnology

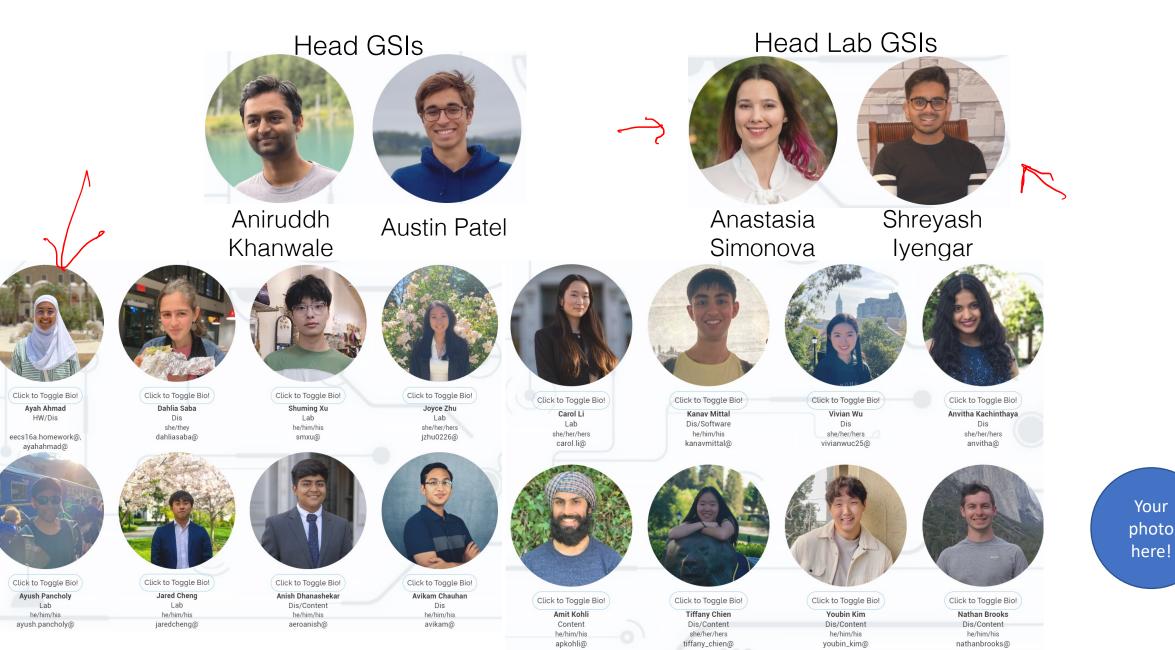

### Course Staff

#### Head GSIs

Aniruddh Khanwale

Austin Patel

#### Head GSIs: eecs16a@Berkeley.edu

Email with: Questions not for Ed, conflicts, accommodations, emergencies, administrative questions

### Course Staff

#### Head GSIs

Aniruddh Khanwale

Austin Patel

#### Head Lab GSIs

Head GSIs: eecs16a@Berkeley.edu Email with: Questions not for Ed, conflicts, accommodations, emergencies, administrative questions

Course manager Great resource for 1-1 concerns Krystle@eecs.Berkeley.edu

Krystle Simon

### Course Staff

# Pathway to becoming like us!

- if you do well in class you can apply to:

- Become an ASE

- Grade homework, assist in labs, tutor and help with office hours

- Become a uGSI

- Lab / Discussion / content

- Become head TA...

- Go to grad school, get a PhD

- Become faculty

- Teach 16A!

### Course policies

- Syllabus is on the course website: <u>https://eecs16a.org/</u>

- You are responsible for reading and following all course policies listed

Ed: <u>edstem.org</u>

a resource for you to help each other out

• Questions? Ask <u>eecs16a@berkeley.edu</u>

## **Grading Policies**

- Midterm 1, Midterm 2 (55 points each)

- Final (100 points)

- Lab mandatory (55 points)\*

- Homework (35 points)

- Exam second-chance policy based on optional Midterm Redo

# Homework (HW)

- Due Fridays at 11:59pm

- HW Party: Fri 9-11am in 'the Woz'

- Office Hours: see course calendar

- HWO due Friday

- You grade, we check!

- Self-grades due the next Friday

- 2 HW drops, 6 'slip days'

<u>Note</u>: Self-grading is not <u>just</u> about us being lazy!! (it is also to help you learn)

We treat all our students with utmost trust and respect and expect students to return the same trust and respect. We will have <u>zero-tolerance</u> for academic dishonesty. <u>No</u> <u>excuses or special circumstances will be considered</u>.

Always seek help, never cheat.

## You are here to learn!

- Learning can be hard and fun

- Collaborate and build community on Ed/HW Party/Study Groups

- Encourage different perspectives this is Berkeley!

- Everyone here is smart

- Students have different backgrounds

- (some) Professors make mistakes feedback helps

- If you are struggling, ask for help!

### How to succeed in 16A

- Get enough sleep

- Attend lecture and discussion

- Do not do the above two at same time

- Actively read notes

- Try HW on your own, early

- Discuss problems with study group and/or at HW Party

- Study with others as well as alone

- Seek and offer help

| study                      |

|----------------------------|

| The act of texting, eating |

| and watching TV with an    |

| open textbook nearby.      |

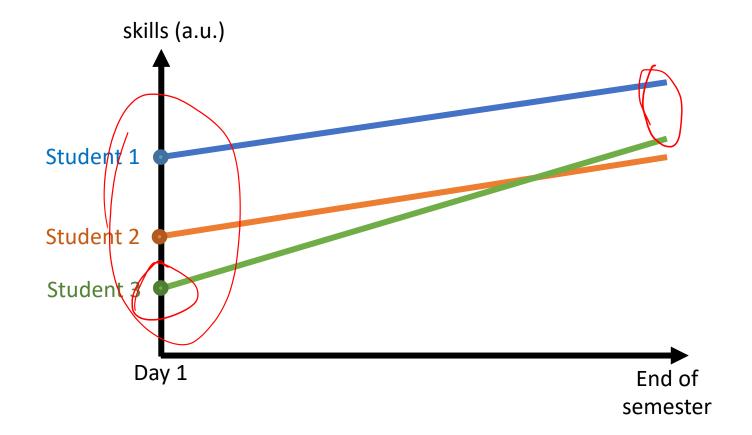

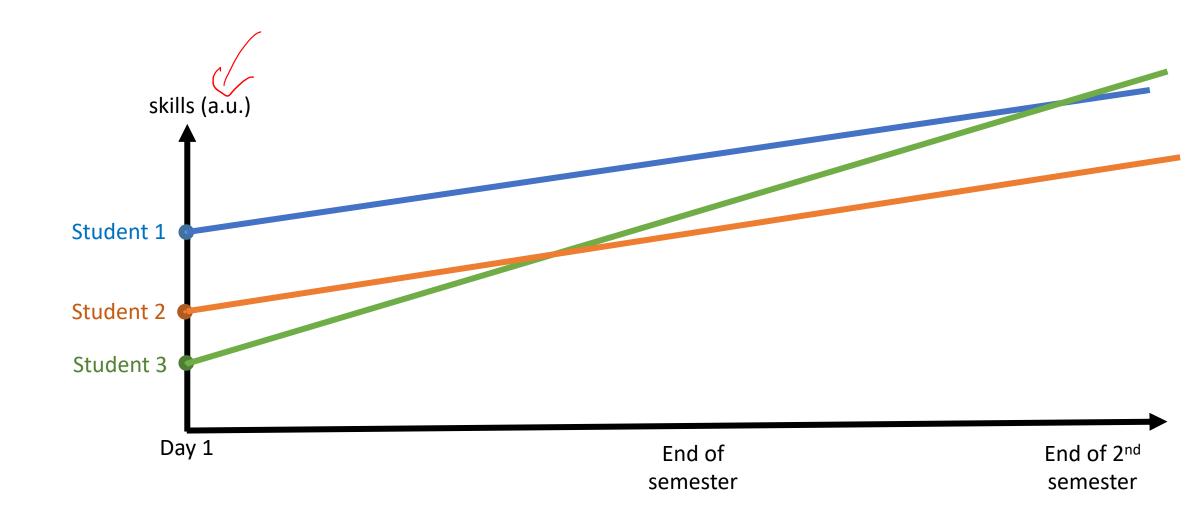

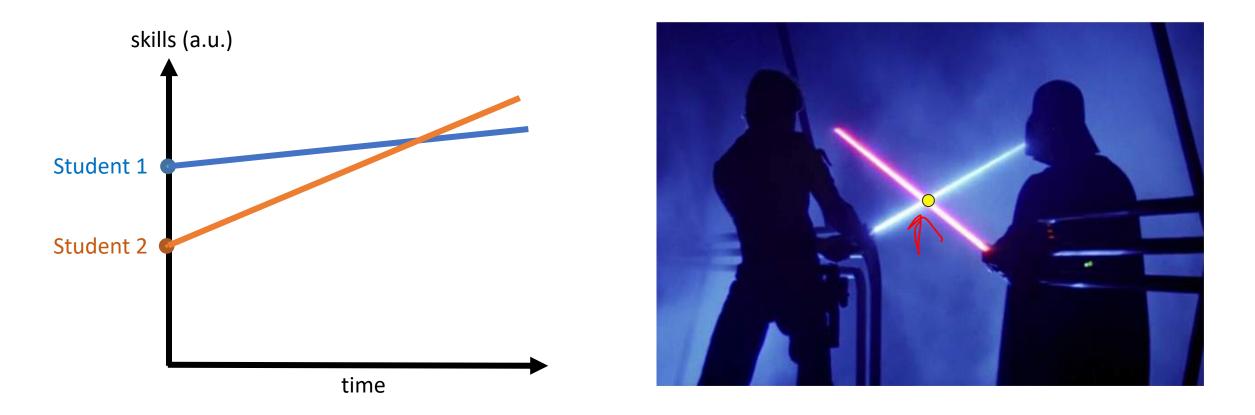

### Slope is more important than intercept

### Slope is more important than intercept

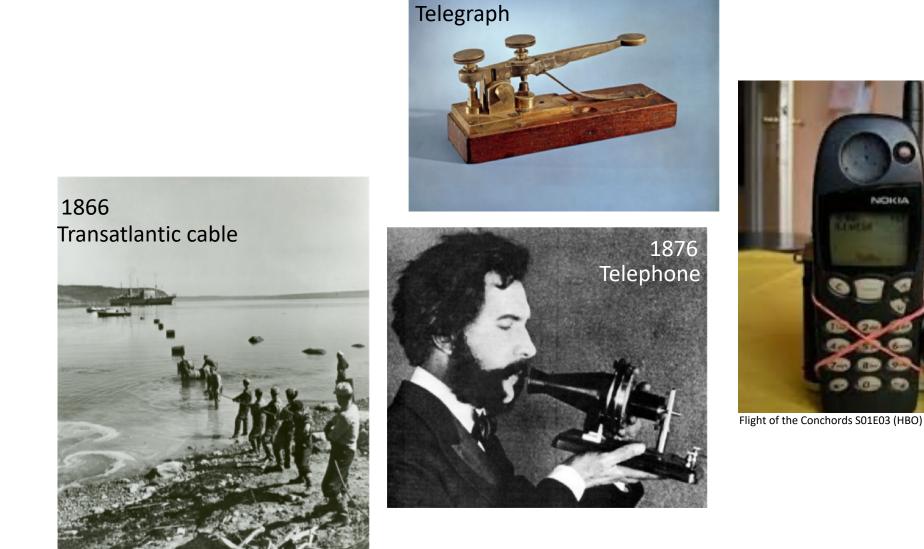

### How did we get from this...

1837

### To this...

BEANS FACEBOOK.COM/SHOEBOXBLOG

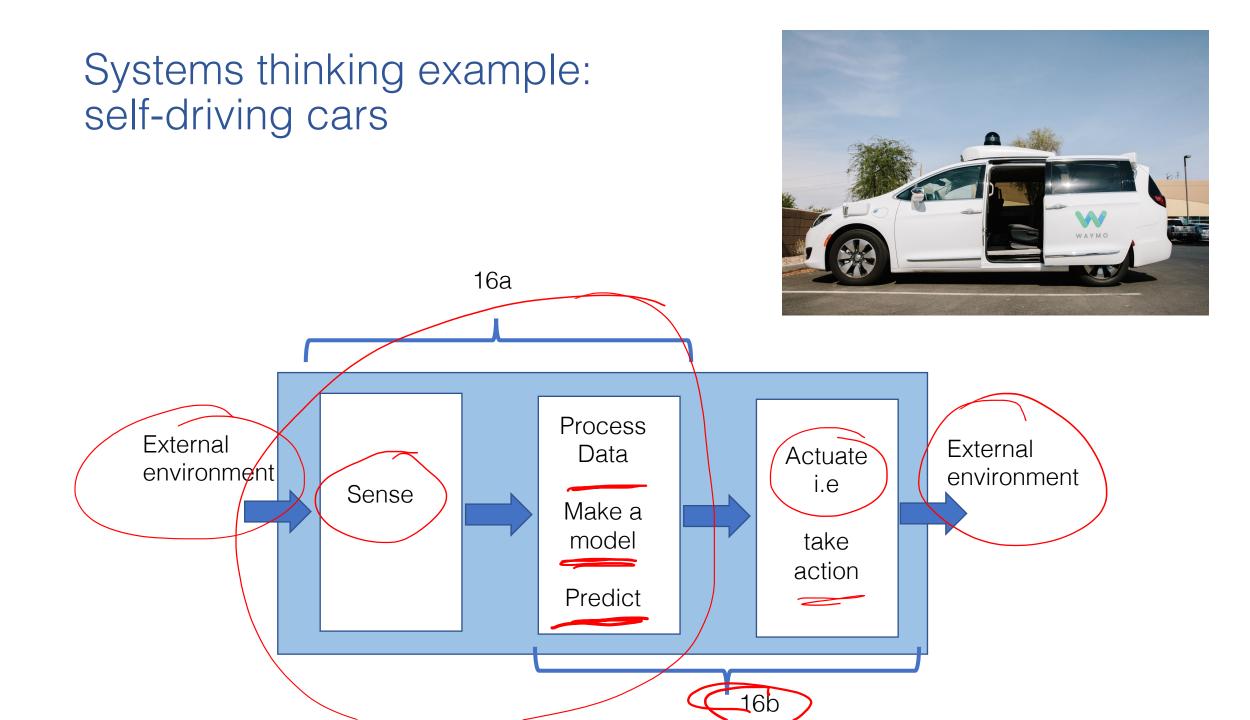

Autonomous cars

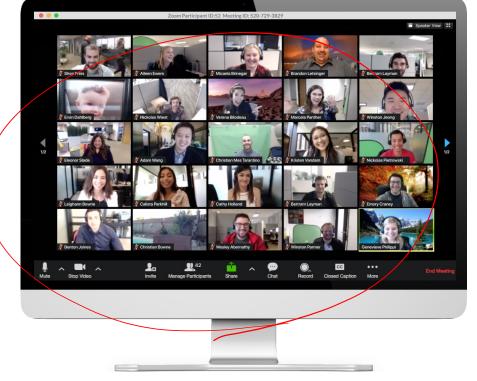

#### A 1000 student class on a computer screen

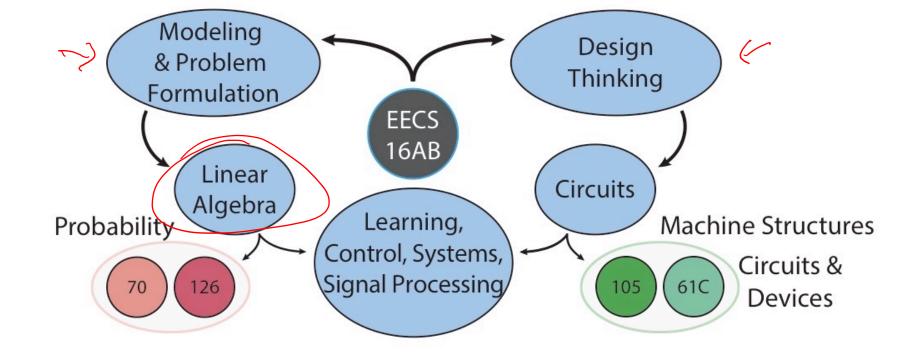

# Learning Goals

To help you understand many nerd jokes:

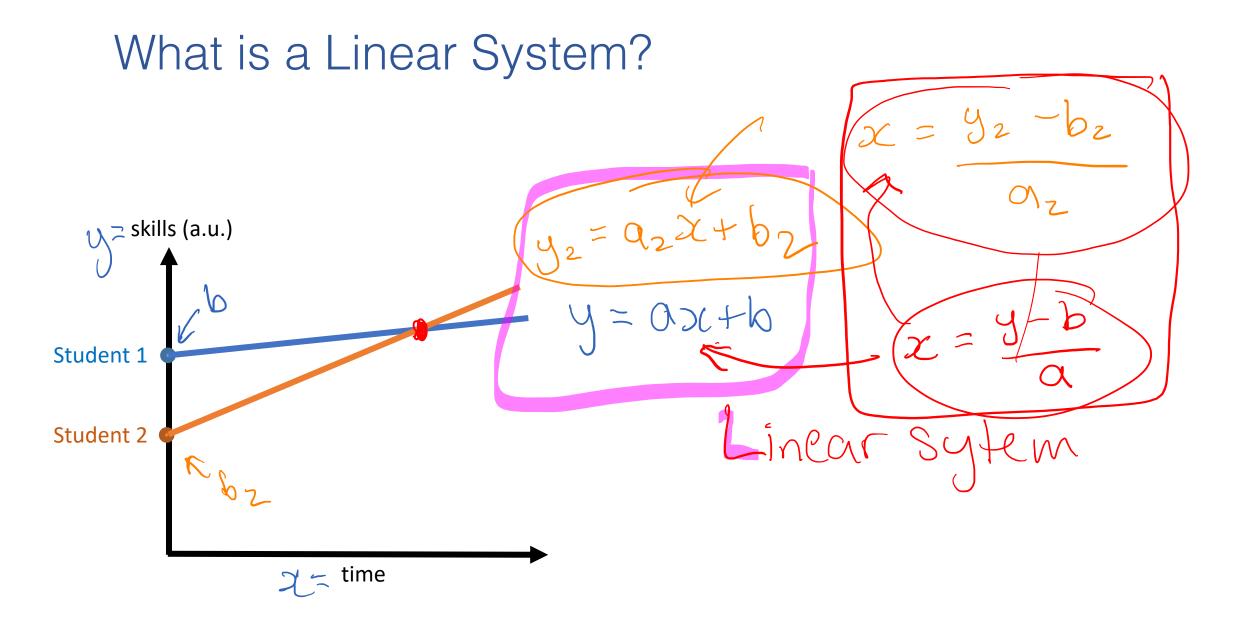

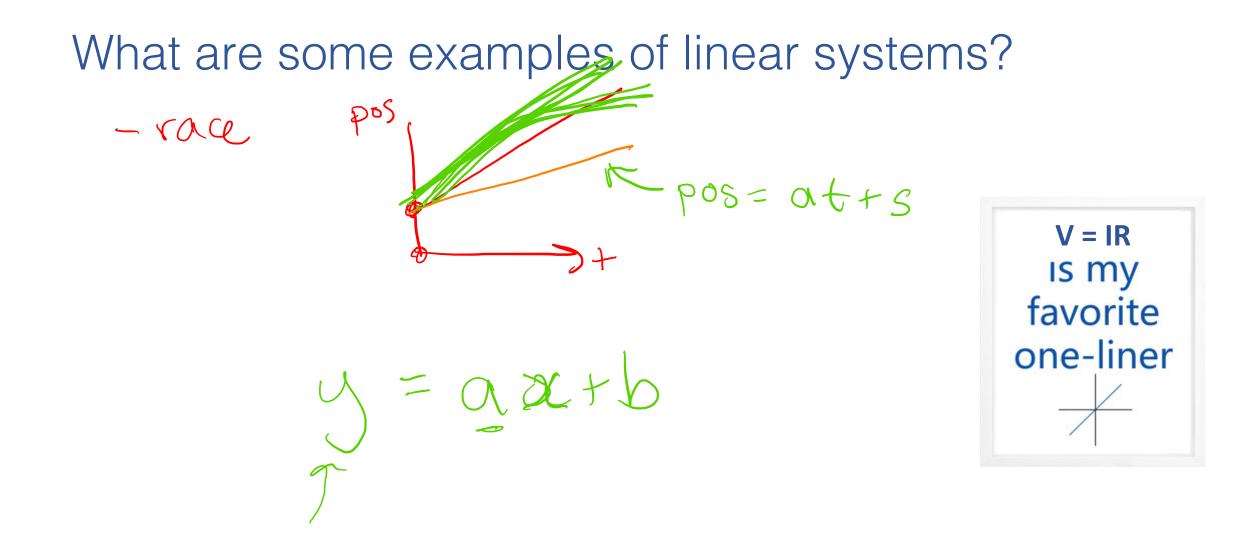

- Module 1: Introduction to linear systems

- Module 2: Introduction to circuits and design

- Module 3: Introduction Signal Processing and Machine Learning

EECS 16B

- Module 4: Advanced circuit design / analysis

- Module 5: Introduction to control and robotics

- Module 6: Introduction to data analysis and signal processing

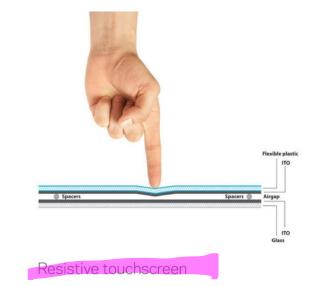

### In the Lab

### How do we solve linear systems of equations?

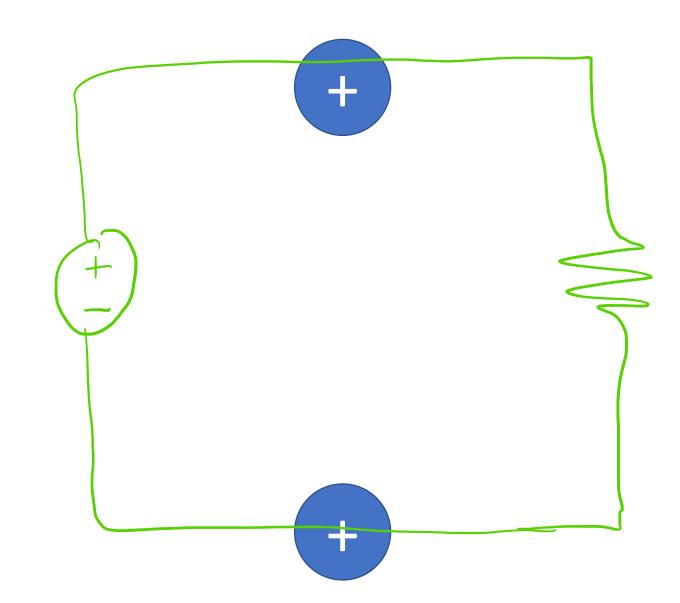

### Electronic Devices Depend on the Movement of Charge

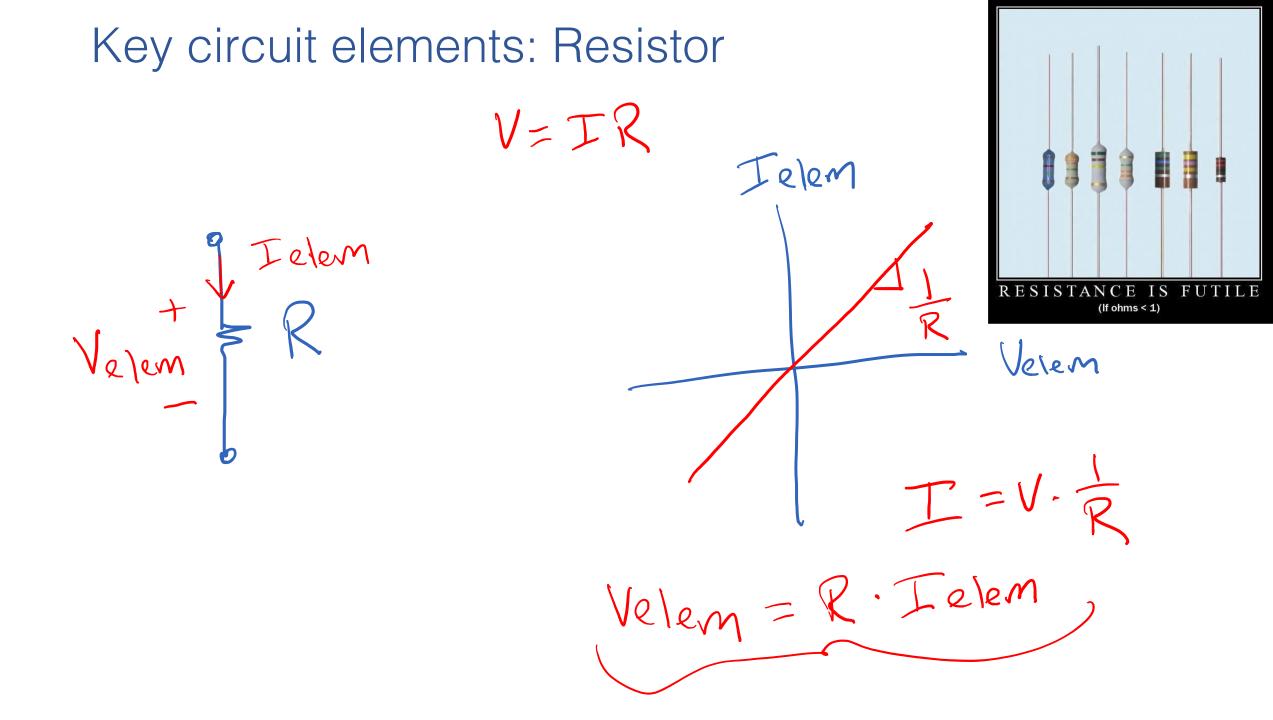

# Electrical Quantities V=TR Ohm's Law

T→ flows through an element V→ force applied across the element R→ opposition to current flow

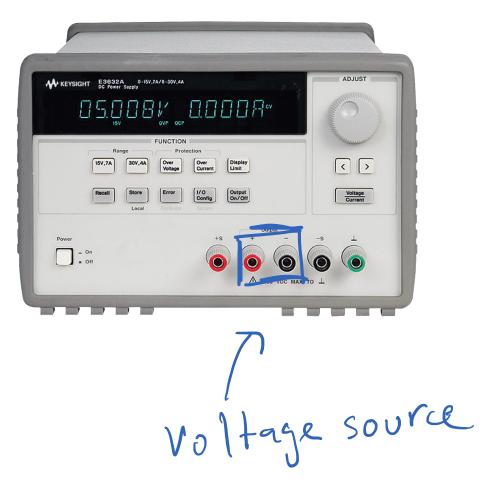

### In the Lab!

51'

Wire

### Circuit Diagram Elements

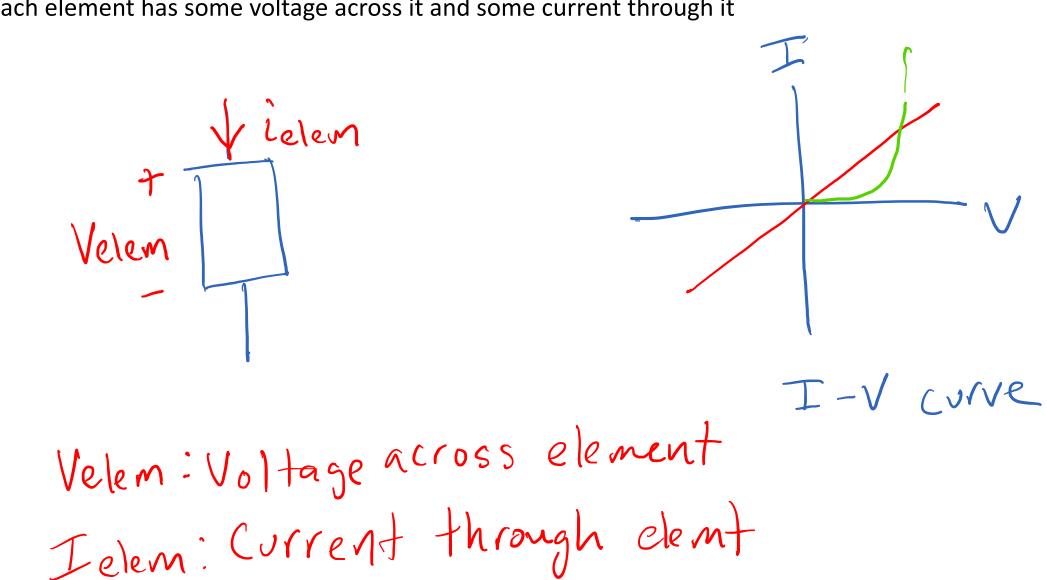

Each element has some voltage across it and some current through it

### Key circuit elements: Voltage Source

+ FIelem n (+) 5V Velem

Velem= 5V

Ielem = ?

You complete me.

Ielem

SV Velen

I is set by external circuit

## Circuit Diagram

Collection of elements, where each element has some voltage across it and some current through it

I = TRV= I. 100 SL L) T = 0.1ANodes: points where elements meet

### Devices as part of a system

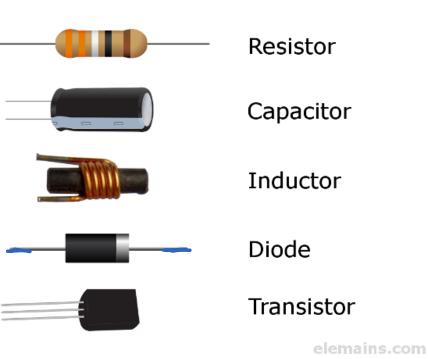

**Discrete Components**

Printed Circuit Board

Surface Mount Components

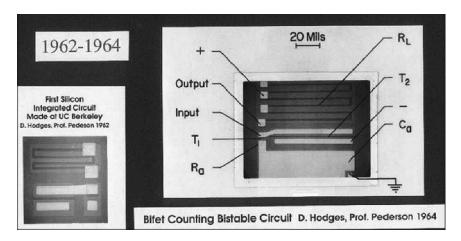

Integrated Circuit

### Transistor

First transistor - Dec 1947

#### First integrated circuit 1958

**Go Bears!**

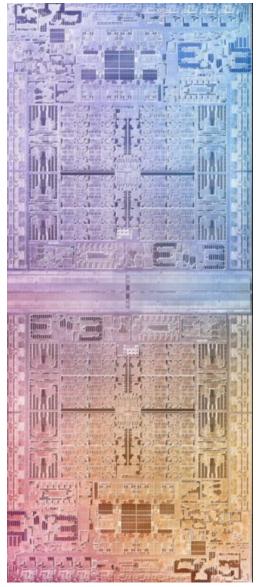

Modern IC: 2022: Apple M1 Ultra Processor 5nm transistors, 114 billion of them!

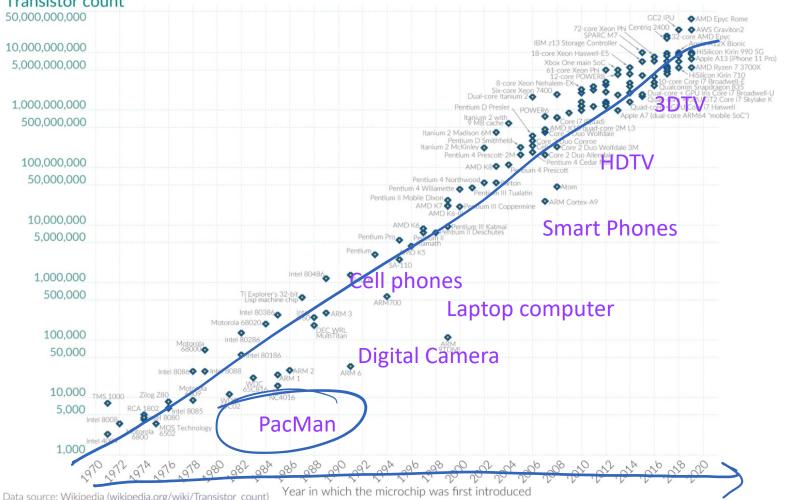

# Computational advances due to fabrication advances

#### Moore's Law: # of transistors in a dense integrated circuit doubles ~every two years.

Gordon Moore

Intel Cofounder

B.S. Cal 1950!

Magazine, 1965

OurWorldinData.org - Research and data to make progress against the world's largest problems.

Licensed under CC-BY by the authors Hannah Ritchie and Max Roser.

#### Moore's Law: The number of transistors on microchips doubles every two years Our World in Data

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important for other aspects of technological progress in computing – such as processing speed or the price of computers.

#### Transistor count

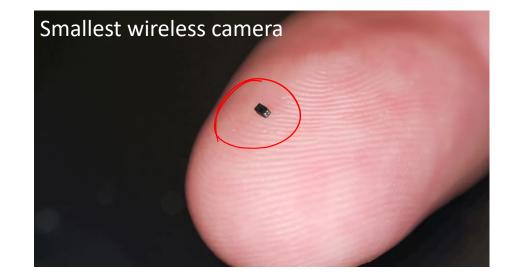

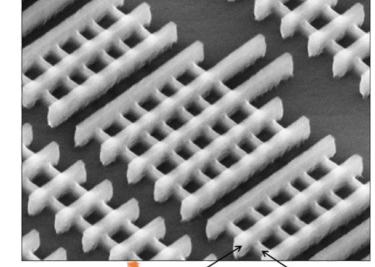

### Sense of Scale

#### Transistors! As small as 5nm!

LOG SCALE

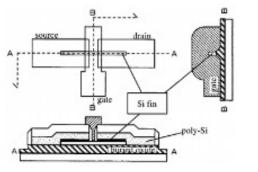

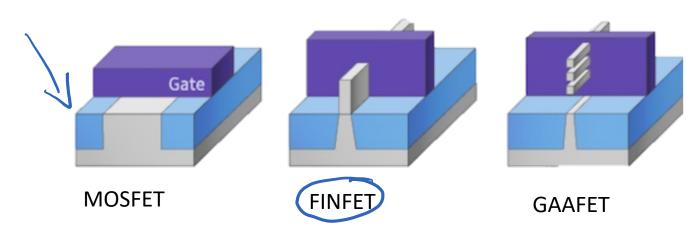

### FinFET

2320

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 47, NO. 12, DECEMBER 2000

#### FinFET—A Self-Aligned Double-Gate MOSFET Scalable to 20 nm

Digh Hisamoto, Member, IEEE, Wen-Chin Lee, Jakub Kedzierski, Hideki Takeuchi, Kazuya Asano, Member, IEEE, Charles Kuo, Erik Anderson, Tsu-Jae King, Jeffrey Bokor, Fellow, IEEE, and Chenming Hu, Fellow, IEEE

Abstract—MOSFETs with gate length down to 17 nm are reported. To suppress the short channel effect, a novel self-aligned double-gate MOSFET, FinFET, is proposed. By using boron-doped  $Si_{0,4}$  Ge<sub>0,4</sub> as a gate material, the desired threshold voltage was achieved for the ultrathin body device. The quasiplanar nature of this new variant of the vertical double-gate MOSFETs can be fabricated relatively easily using the conventional planar MOSFET process technologies.

Index Terms—Fully depleted SOI, MOSFET, poly SiGe, shortchannel effect.

I. INTRODUCTION

T O DEVELOP sub-50-nm MOSFETs, the double-gate structure has been widely studied. This is because

Fig. 1. FinFET typical layout and schematic cross sectional structures.

### **Go Bears!**

Prof. Tsu-Jae King Liu Pro

Prof. Chenming Hu (left)

Prof. Jeff Bokor

### Completing the puzzle... coding!

Ada Lovelace wrote the first computer program

Alan Turing figured out how to build a computer to execute programs

**Claude Shannon** Information theorist

### Module 1: Imaging