# Latch timing and SRAMs

Discussion 8

### **Announcements**

- Design review 4/8 /

- Homework 4 due 4/12

- Lab 5 due 4/12

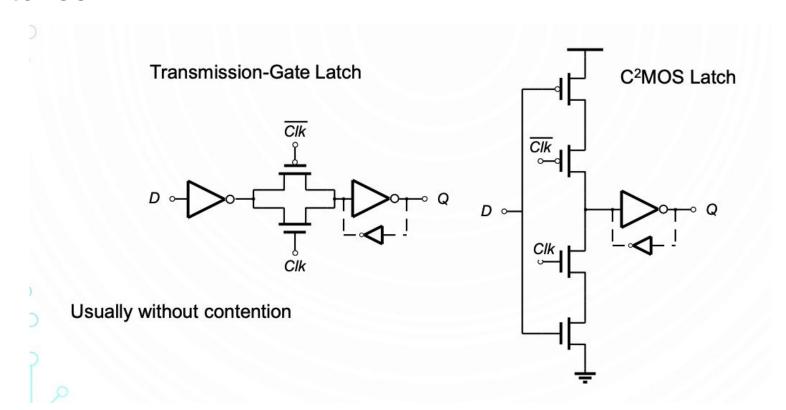

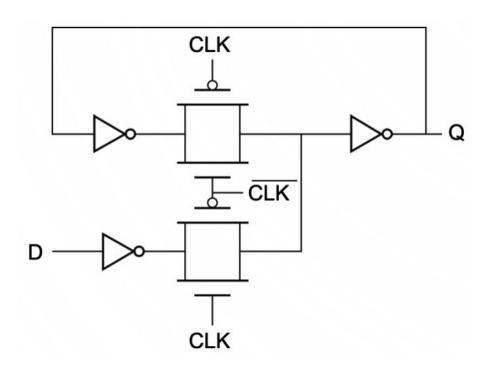

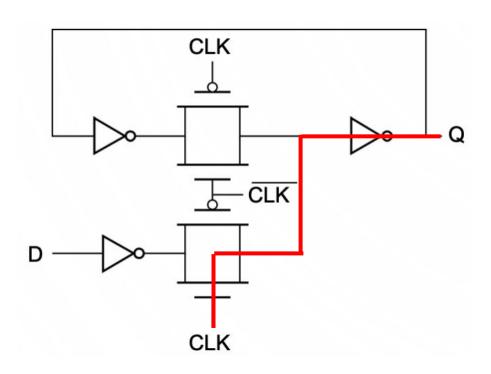

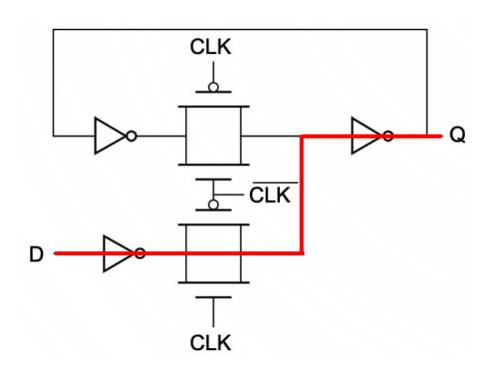

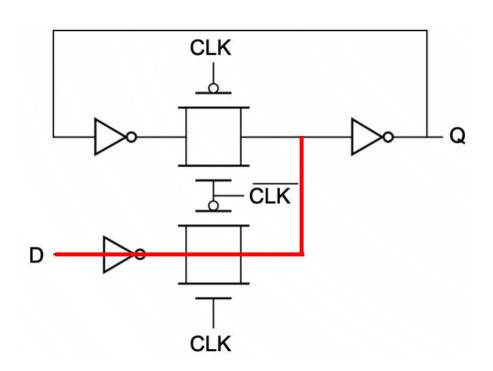

# Latches

Where are the important paths?

Clk-Q path:

D-Q path:

Setup path:

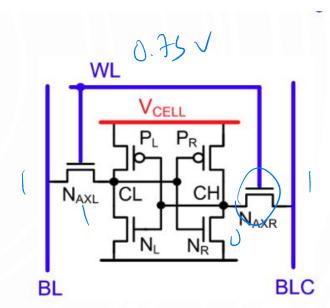

# 6T SRAM cell

#### **SRAM** assists

- Dynamically change voltages

- Negative BL helps with writing

- Lower VDD (V<sub>CELL</sub>) helps with writing

- Higher WL helps with writing, lower hurts

- Lower WL helps with read, higher hurts

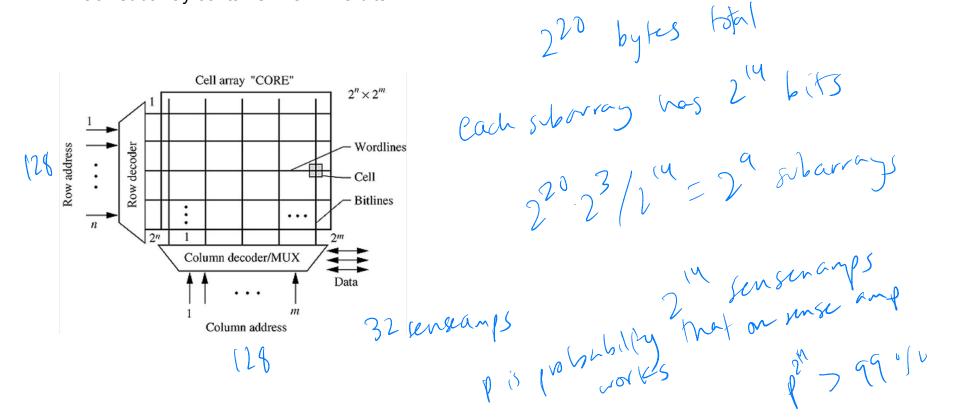

# Homework 4 Problem 2 (2023)

#### 2. SRAM yield

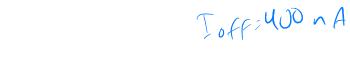

We will analyze a 2MiB (i.e.  $2^{20}$  Bytes) SRAM array, consisting of 128 x 128 bit subarrays. Four columns share one sense amplifier. Bitline capacitance is 1pF and the supply is 1V. For this problem, assume that all the SRAM cells in the array are identical (i.e. not affected by the random process variation) and  $I_{on} = 100\mu\text{A}$ ,  $I_{off} = 400\text{nA}$ . Assume that the target access time of 1ns is dominated by the bitline discharge.

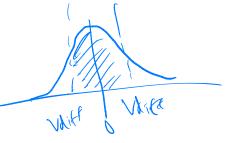

If the sense amplifier offset has normal distribution, with zero mean and standard deviation of 15mV, would you expect this array to have a high yield? How many redundant columns would need to be added per subarray to have >99% yield for the whole 2MB SRAM array (note that you may not have to do the exact calculation of this)?

# **SRAM Topology: Subarray**

• Each subarray contains 128 x 128 bits

# SRAM Topology: Shared Sense Amp

4 columns share 1 sense amp

- rdwdent Guskamp?.

32 anst apps

[ ] 32 + ([-p) p. 32

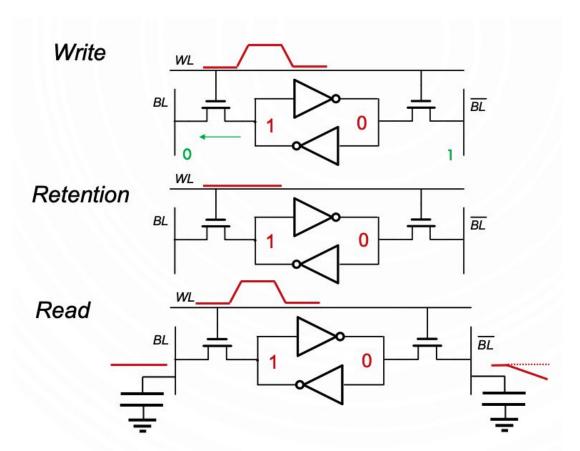

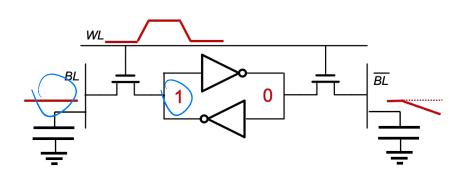

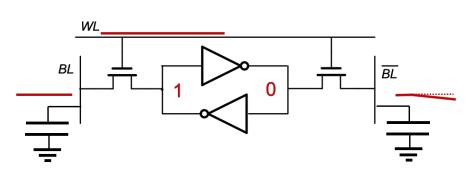

## **SRAM** Read

WL enabled

WL disabled

# Yield Computation (without redundancy)

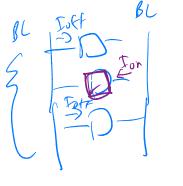

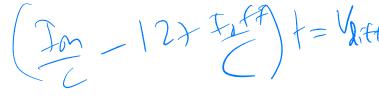

- Compute worst-case differential bitline voltage V<sub>BI</sub>

- 2. Compute required sense amp offset for read failure

- 3. Find probability of single sense amp failing during read (sense amp yield)

- 4. Find subarray yield

- Probability of all sense amps working (or 0 sense amps failing)

- 5. Find SRAM array yield

- Probability of all subarrays working

## Yield Computation (with K redundant columns)

- 1. Compute worst-case differential bitline voltage  $V_{\scriptscriptstyle BL}$

- 2. Compute required sense amp offset for read failure

- 3. Find probability of single sense amp failing during read (sense amp yield)

- 4. Compute number of redundant sense amps L

- 5. Find subarray yield

- Probability of 0 sense amps failing or 1 sense amp failing or ... or L sense amps failing

- Find SRAM array yield

- Probability of all subarrays working