# NTU 6342 / EE 241 Homework #2 Solutions

## Problem 1:

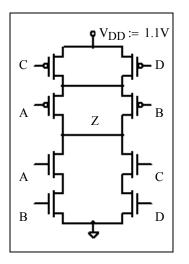

For the CMOS implementation:

$$t_p \coloneqq \frac{t_{pHL} + t_{pLH}}{2} \qquad \qquad t_p = 39.059 \text{ ps}$$

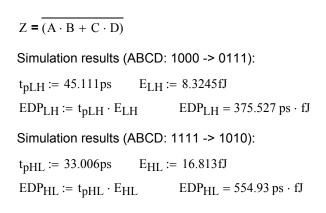

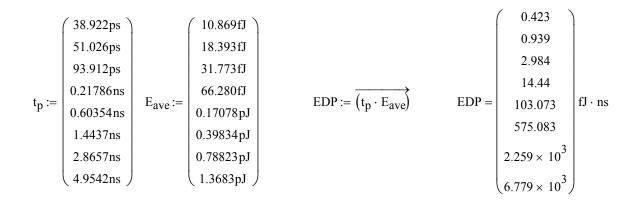

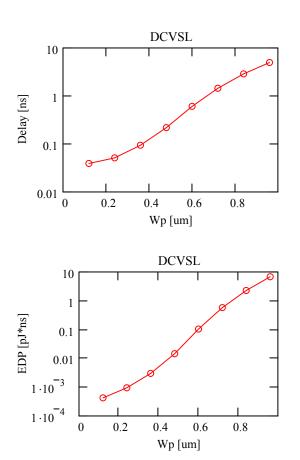

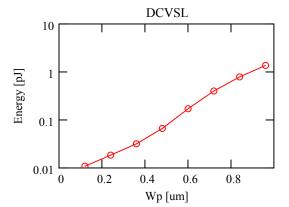

For the DCVSL implementation:

Minimum width is optimal.

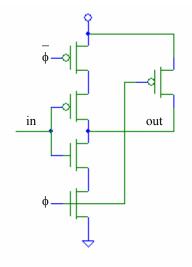

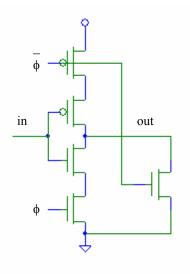

Modified DCVSL Implementation:

For small sizes of the PMOS keepers, the output nodes before the inverters will not be able to reach logic '1'. However, if the leakage of the PMOS keepers are large enough, then the leakage current may be able to charge up these nodes. Problem #2:

Part a:

Pulse Static CMOS XOR Gate

$$A \oplus B = \overline{A} \cdot B + \overline{B} \cdot A = (\overline{(A \cdot \overline{B})} \cdot \overline{(\overline{A} \cdot B)}) = \overline{[(\overline{A} + B) \cdot (A + \overline{B})]}$$

$$A = \overline{A} + \overline{B} + \overline{B} \cdot A = (\overline{(A \cdot \overline{B})} \cdot \overline{(\overline{A} \cdot B)}) = \overline{[(\overline{A} + B) \cdot (A + \overline{B})]}$$

$$A = \overline{A} + \overline{B} + \overline{B} + \overline{A} = (\overline{A} + \overline{B}) + \overline{A} + \overline{B} + \overline{B} + \overline{A} + \overline{B} + \overline$$

a - clocked inverter with reset high

b - clocked inverter with reset low

Part b:

Optimize each gate for the required transition:

Inverter c: optimize for low to high transition

$$W_n = \frac{W_p}{4} \qquad \qquad g_c := \frac{5}{6}$$

NOR d: optimize for high to low transition

$$W_n = W_p$$

$g_d := \frac{2}{3}$

NAND e: optimize for high to low transition

$W_n = 2 \cdot W_p$   $g_e := 1$

$$G := g_c \cdot g_d \cdot g_c \cdot g_e \qquad G = 0.463$$

Assume that the XOR gate drives a fanout of 4 inverters with the same size as c1:

F := 4 N := 4

H := G · F H = 1.852 h :=

$$\sqrt[N]{H}$$

h = 1.167

Assume c1 is unit sized:  $c_1 := 1$

$$d := \frac{h}{g_d \cdot g_c} \qquad d = 2.1 \qquad c_2 := \frac{h}{g_c} \cdot d \qquad c_2 = 2.939$$

$$e := \frac{h}{g_c} \cdot c_2 \qquad e = 3.429 \qquad \text{load} := h \cdot e \qquad \text{load} = 4$$

Sizes:

ge

$$c_1 = 1$$

$d = 2.1$   $c_2 = 2.939$   $e = 3.429$

Note that due to the limitation of the pulsed static CMOS logic family's ability to optimize only successive NAND-NOR chains, effectively one big AND function, the last gate NAND(e) is being optimized for the wrong transition (high-to-low instead of low-to-high, where the parallel transistors are).

This is due to the fact that the XOR function cannot be decomposed into purely AND components.

Problem #3:

$V_{th} := 300 \text{mV}$

Part a:

If we assume that the switching threshold of the output inverters are at half the supply voltage:

Given

$$V_{dd} - 3 \cdot V_{th} = \frac{V_{dd}}{2}$$

$$V_{dd} := Find(V_{dd}) \qquad V_{dd} = 1.8 V$$

Part b:

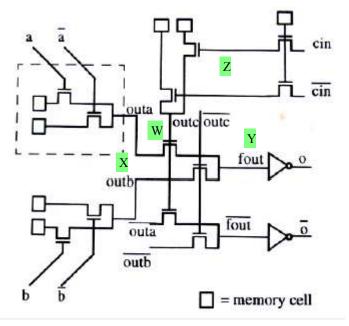

From the memory cell to node X, the time constant is:

$\tau_1 = \mathbf{R} \cdot \mathbf{3} \cdot \mathbf{C}_d$

From node X to node Y:

$\tau_2 = \mathbf{R} \cdot \left( 2 \cdot \mathbf{C}_d + \mathbf{C}_{inv} \right)$

From the cin to node Z (assuming that this signal is also used to generate the complement of outc):

$\tau_3 = R \cdot \left( C_d + 2 \cdot C_g \right)$

From the memory cell to node W:

$$\tau_4 = \mathbf{R} \cdot \left( 2\mathbf{C}_d + 2\mathbf{C}_g \right)$$

It can be seen that the worst case delay will be from cin to the output:

$t = K_2 \cdot \tau_2 + K_3 \cdot \tau_3 + K_4 \cdot \tau_4 + t_{inv}$

Since node X only goes to Vdd - Vtn:

$$K_{2} = \ln \left[ \frac{V_{dd} - V_{tn}}{\left(V_{dd} - V_{tn}\right) - \frac{V_{dd}}{2}} \right]$$

$$K_3 = K_4 = \ln(2)$$

If we assume that the gate capacitances dominate, then the transistors which are driving gates should be made wider, to reduce their channel resistance, and transistors whose gates are driven by other pass gates should be smaller to reduce their gate capacitances.

## Part c:

Since the input to the inverter loses 3 threshold voltages, the inverter PMOS cannot be fully turned off, thus resulting in static current flowing, increasing the total power dissipation.

### Part d:

To prevent the 3 threshold voltage drop at the input of the inverter, transmission gates could be used.

This presents increased input capacitances to the driving gates, as well as increased silicon area, and potentially, more S/D leakage due to increased transistor count.

To eliminate the static power consumed by the inverter due to the partially "on" PMOS, a keeper can be introduced at the input of the inverter, controlled by the inverter output.

This approach can result in increased inverter input and output loading due to the added PMOS pull-up. Additional sizing constraints are also introduced into the pass transistor chain design to make sure the inverter input node can be pulled down to ground.

#### Part e:

Decreasing the threshold voltages would result in less static power dissipation in the output inverters, as well as an increase in dynamic power due to the larger voltage swings at the output of the pass transistors.

In addition, if the threshold voltages are made sufficiently low making the transistors harder to turn off, then current can flow through "sneak paths" formed. Due to the bidirectional nature of the pass transistors, current flow is not limited from the input to the output but also in the reverse direction.