### Pipelined A/D Converter

- Model

- Digital Correction

- Digital Calibration

A/D DSP EECS 247 Lecture 18: Pipelined ADC

$$V_{res} = G(V_{in} - DV_{ref})$$

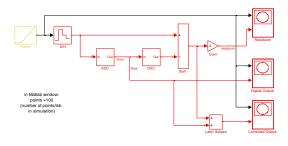

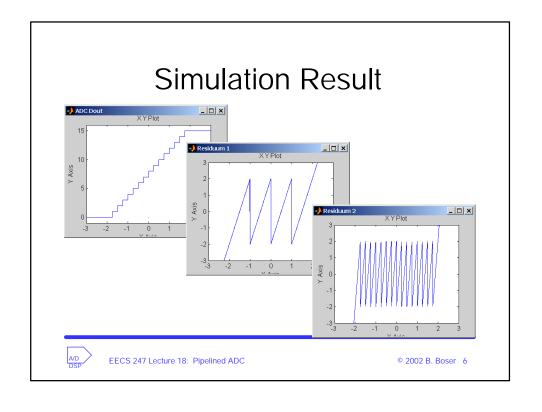

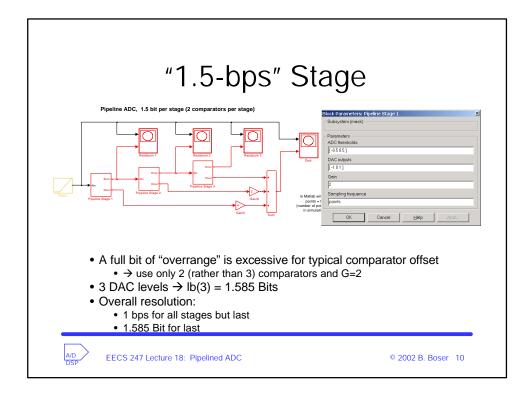

See Matlab/Simulink L18\_pipe\_3\_el.mdl

A/D DSP

EECS 247 Lecture 18: Pipelined ADC

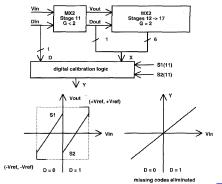

#### Digital Gain Calibration

· Operation of the pipeline stage:

$$V_{res} = G(V_{in} - DV_{ref})$$

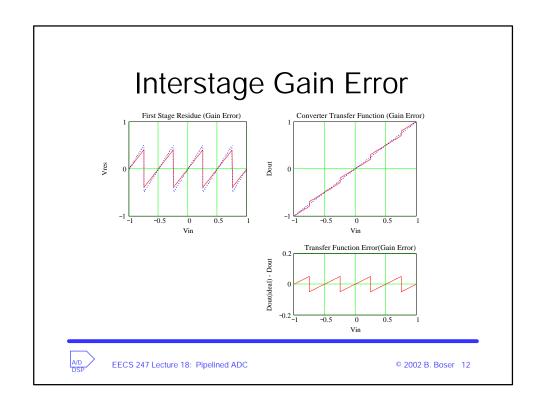

The gain G is off from it's correct value (e.g. 1.8 instead of 2)

· Digital output from the ADC

$$GV_{in} = DGV_{ref} + V_{res}$$

- Gain error (GV<sub>in</sub> term)

- Nonlinearity at segment boundary (DGV<sub>ref</sub> term)

EECS 247 Lecture 18: Pipelined ADC

© 2002 B. Boser 13

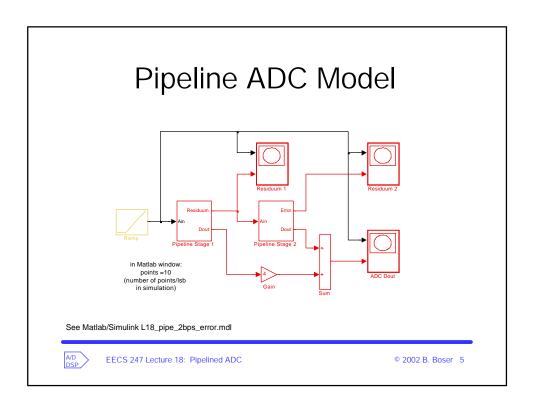

#### Digital Gain Calibration

$$GV_{in} = DGV_{ref} + V_{res}$$

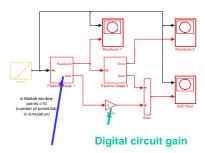

- The "digital" gain in the circuit at right is still 2

- The actual amplifier gain in stage 1 is smaller or larger due to component mismatch

Hence the overall output is incorrect, regardless of the accuracy of stage 2

Analog circuit gain

EECS 247 Lecture 18: Pipelined ADC

## Measuring GV<sub>ref</sub>

- If we knew the value of GV<sub>ref</sub>, we could use use that in our digital logic, rather than G=2

- How can we measure GV<sub>ref</sub>?

$$\begin{split} V_{resA} &= V_{res} \big( V_{in} = V_x, D = 0 \big) = GV_x \\ V_{resB} &= V_{res} \big( V_{in} = V_x, D = 1 \big) = GV_x - GV_{ref} \\ V_{resA} - V_{resB} &= GV_{ref} \end{split}$$

- If we proceed from the back of the pipeline, we can use the already calibrated backend to digitize GV<sub>ref</sub>!

- The measurement is performed once at startup, the values stored in a small RAM (one per stage for 1-bps stage resolution)

- The digital logic uses adders to sum up the different values of GV<sub>ref</sub> from the table stored in the RAM

A/D DSP EECS 247 Lecture 18: Pipelined ADC

© 2002 B. Boser 15

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 28, NO. 12, DECEMBER 1993

1207

# A 15-b 1-Msample/s Digitally Self-Calibrated Pipeline ADC

Andrew N. Karanicolas, Member, IEEE, Hae-Seung Lee, Senior Member, IEEE, and Kantilal L. Bacrania, Member, IEEE

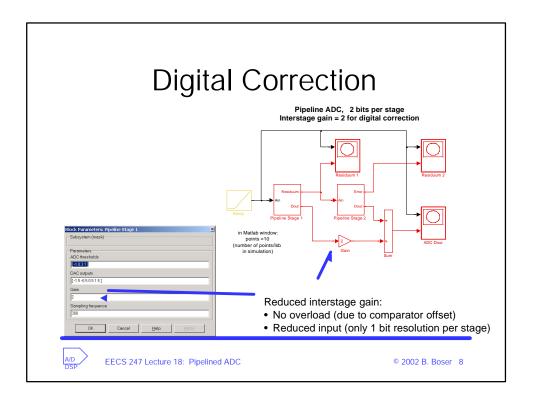

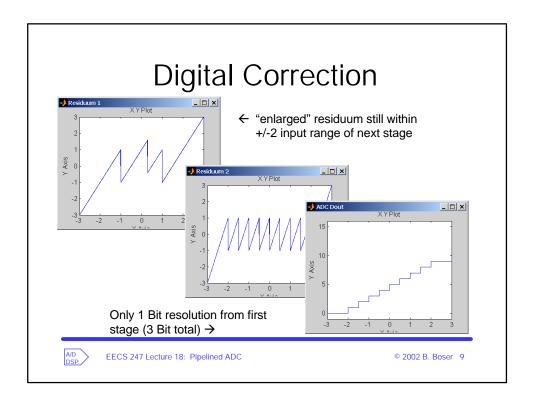

- 1-Bit per stage

- Only 1 comparator per stage

- G<2 to avoid overload in presence of comparator offset

- Digital gain calibration

A/D DSP

EECS 247 Lecture 18: Pipelined ADC